Pipeline MIPS #1

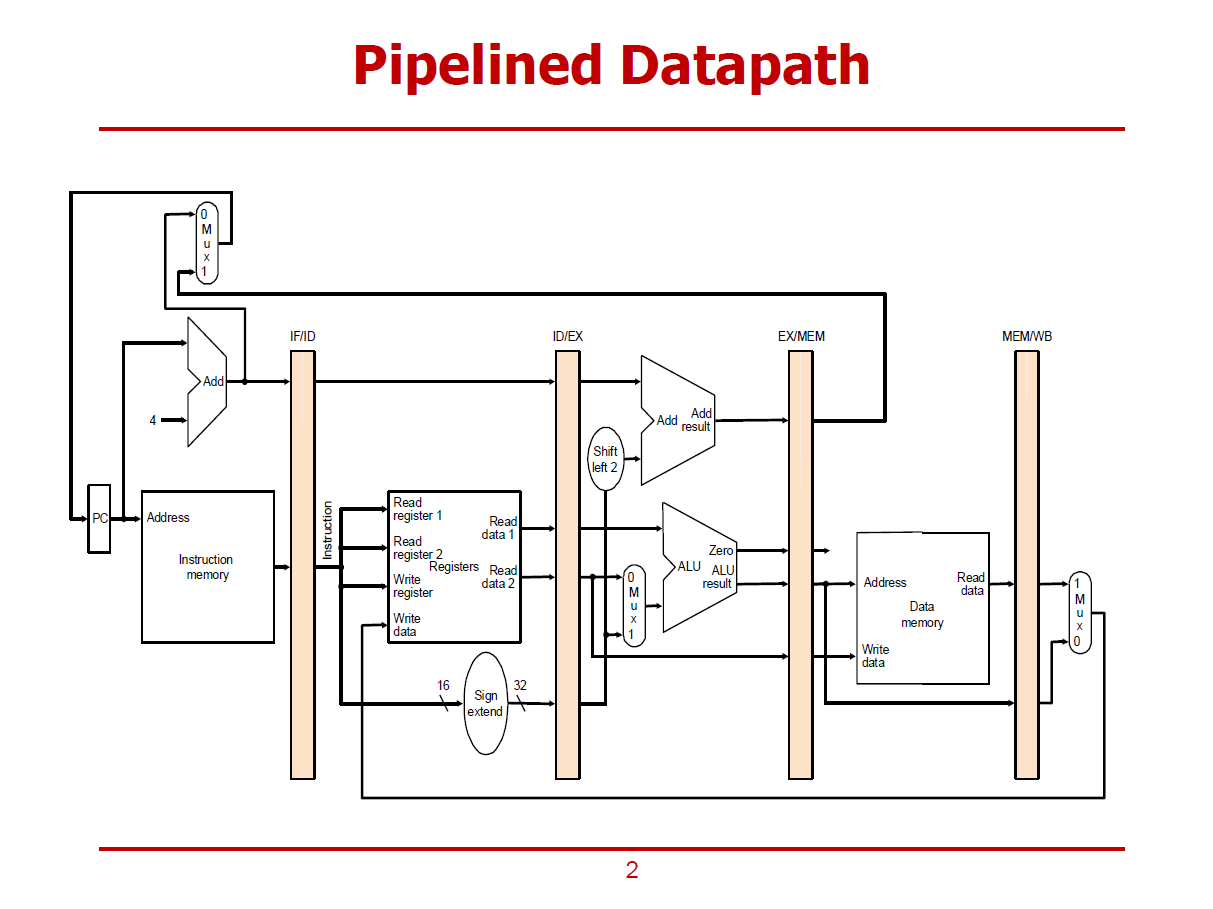

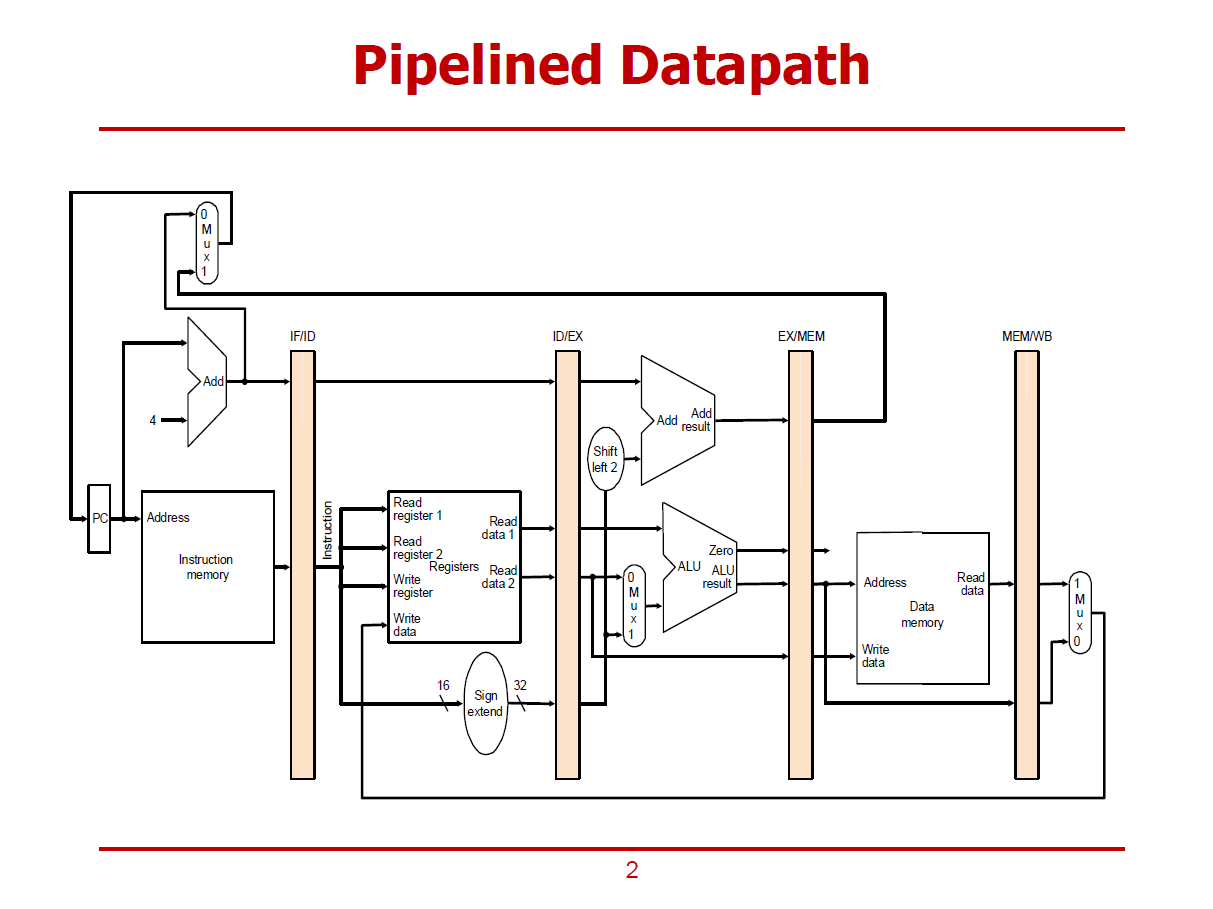

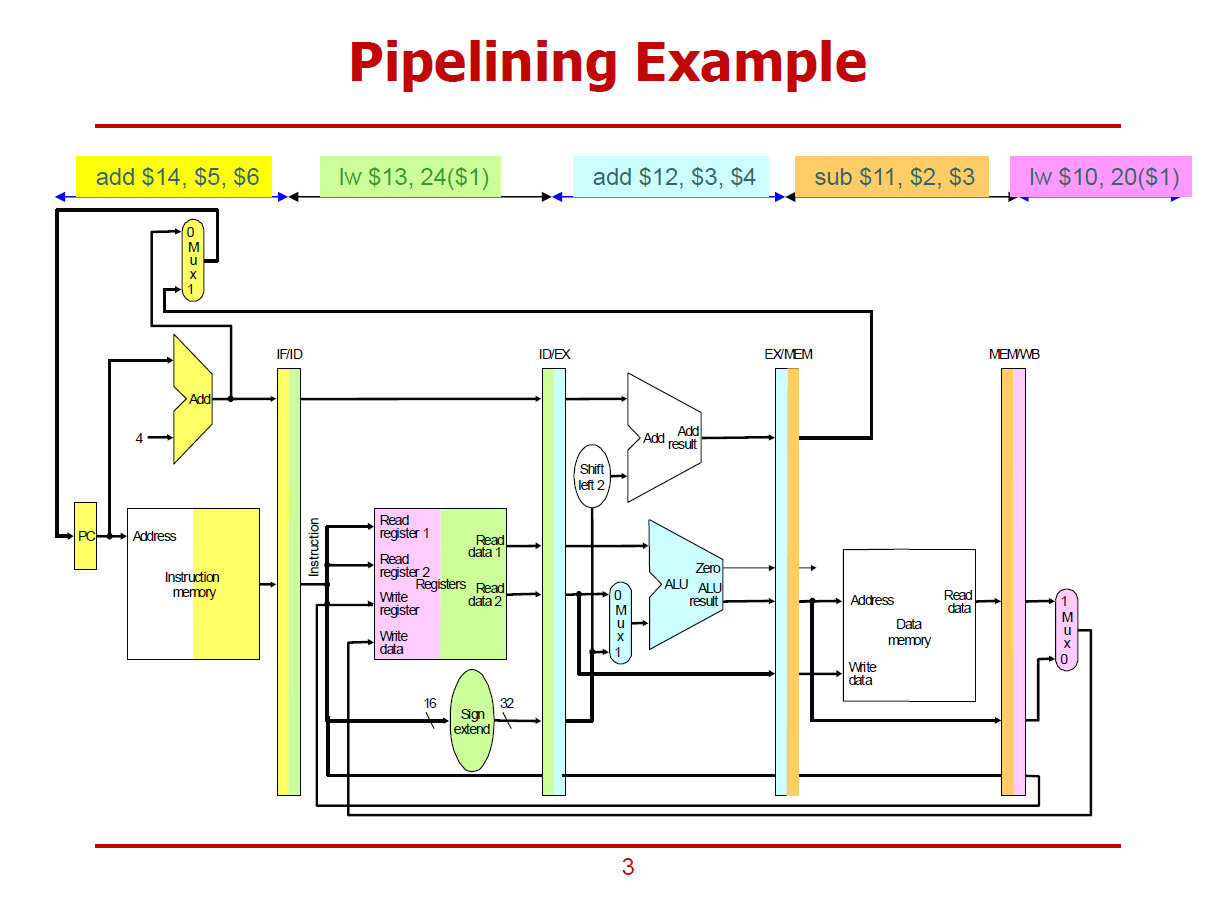

- 회로내에 위치한 살구색 바는 Clock 신호에 동기화 된 다수의 Flip-Flops들로 구성된 Pipeline Register를 간단히 표현한 것이다.

- Pipeline Register은 범용 레지스터의 한 종류라 볼 수 있다.

- WB Stage 이후에는 파이프라인 레지스터가 없는 것을 확인할 수 있는데 이는, WB Stage에서는 레지스터에 값을 바로 쓰고 끝내기 때문에 별도의 파이프라인 레지스터가 필요하지 않다.

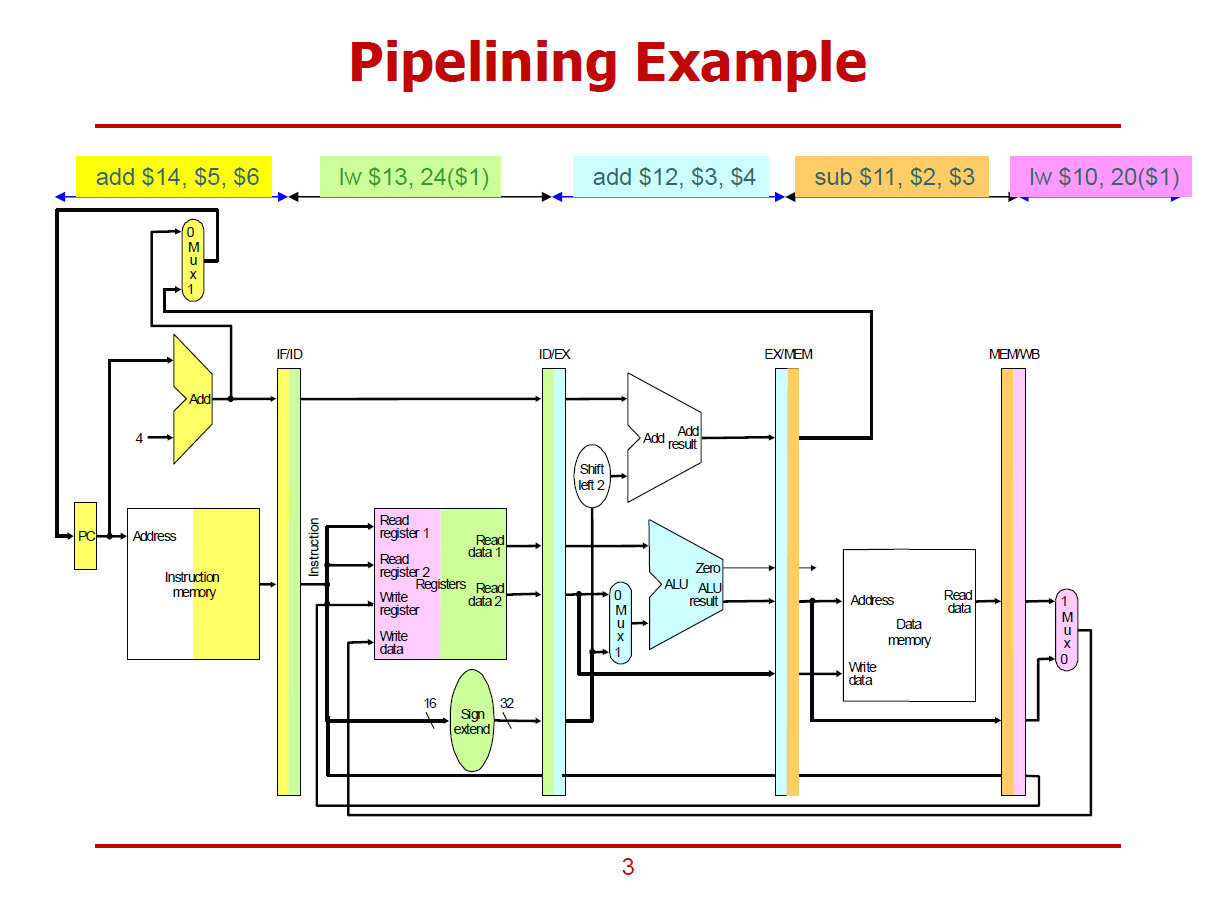

- 5개의 명령어가 제각기 다른 Stage를 처리하고 있는 모습을 표현한 그림이다. (해저드는 고려하지 않은 형태이다.)

- 위 그림에 해당되는 MIPS Assembly Code는 아래의 형태에 가까울 것이다.

\(\texttt{lw \$10, 20(\$1) ! IF Stage, 가장 먼저 실행된 명령어}\)

\(\texttt{sub \$11, \$2, \$3 ! ID Stage}\)

\(\texttt{add \$12, \$3, \$3 ! EX Stage}\)

\(\texttt{lw \$13, 24(\$1) ! MEM Stage}\)

\(\texttt{add \$14, \$5, \$6 ! 가장 늦게 실행된 명령어}\)

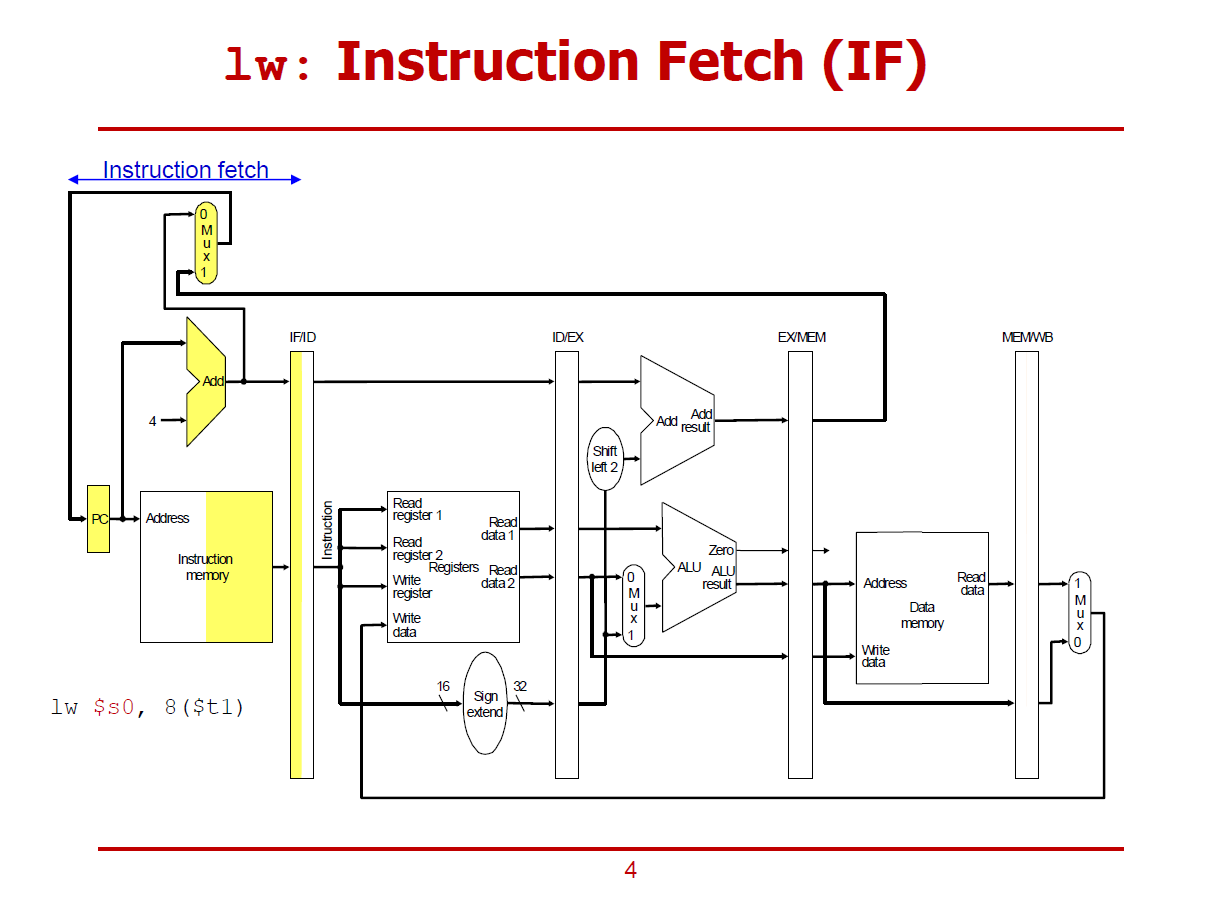

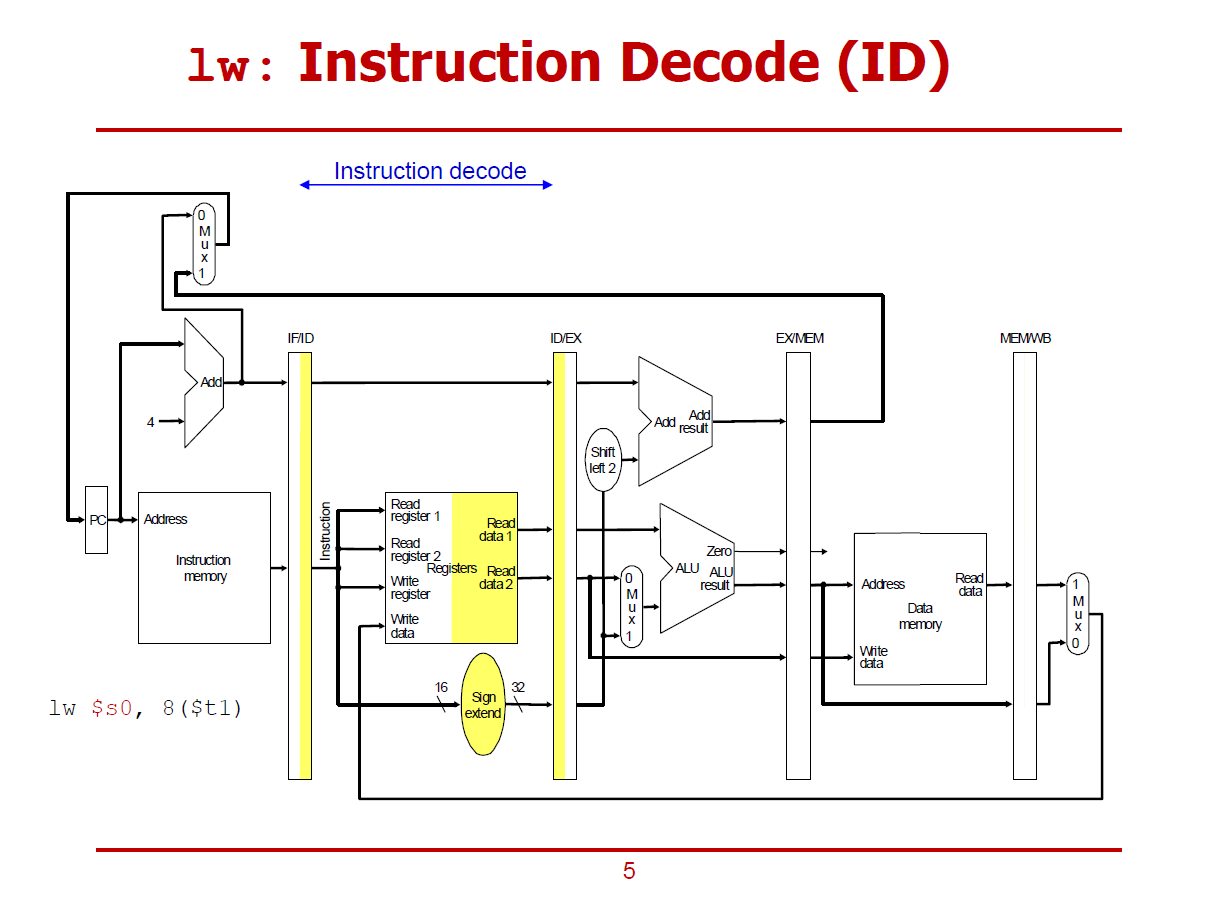

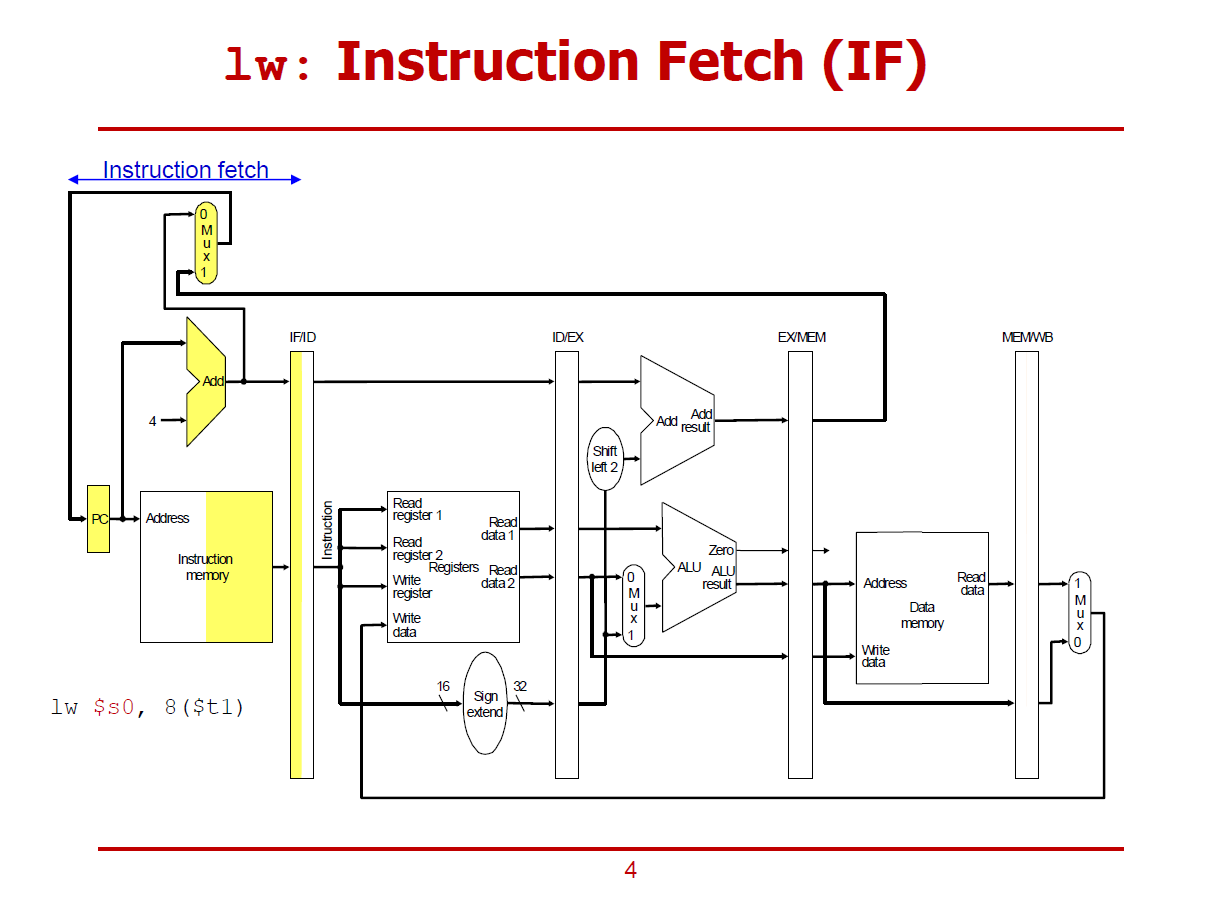

- \(\texttt{lw \$s0, 8(\$t1)}\) 명령어가 파이프라인 기반 MIPS H/W에서 동작되는 원리를 살펴본다.

- IF/ID 파이프라인 레지스터는 Instruction Memory에서 PC값에 해당되는 위치에 저장된 32bit 명령어를 가져오게 된다.

- IF/ID 파이프라인 레지스터는 또한, PC + 4에 해당되는 값을 입력받는다. (이는 명령어가 분기 명령어로 해석될 경우에 대비하여, 분기 주소 계산에 이용하기 위해 입력받는 것이다.)

- IF Stage에서는 Fetch한 명령어가 어떤 명령어인지 모르는 상태로 IF/ID 파이프라인 레지스터에 저장해놓게 된다.

- PC 또한 범용 레지스터이기 때문에, Clock 신호에 맞춰서 값을 입력받게 된다.

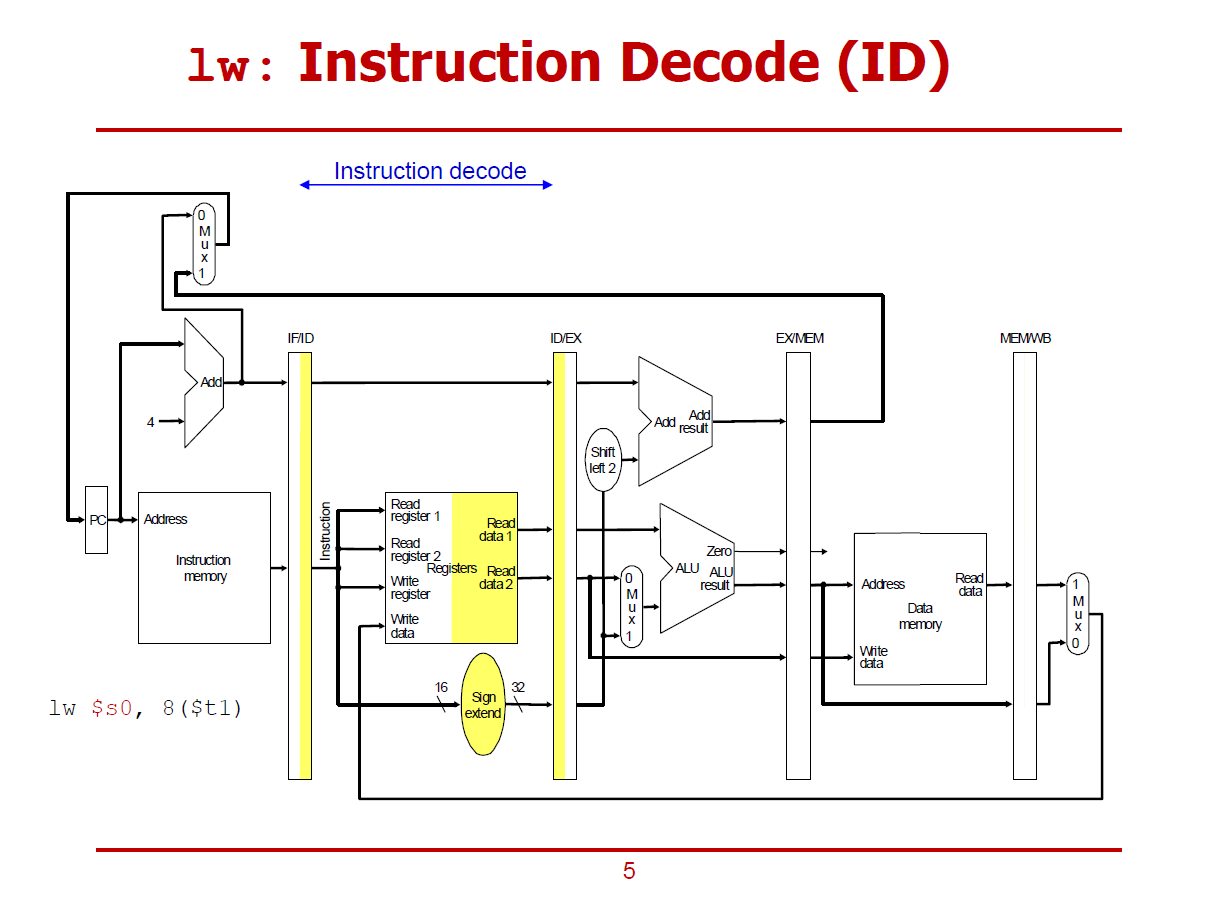

- Clock 신호가 들어오면, IF/ID 파이프라인 레지스터로부터 32bit의 명령어와 PC+4를 넘겨받게 된다.

- 32bit 명령어를 \(\texttt{lw}\) 명령어로 해석되는 절차는 그림에서 생략되었다.

- 레지스터 파일은 오로지 읽기 위해서만 접근하게 된다.

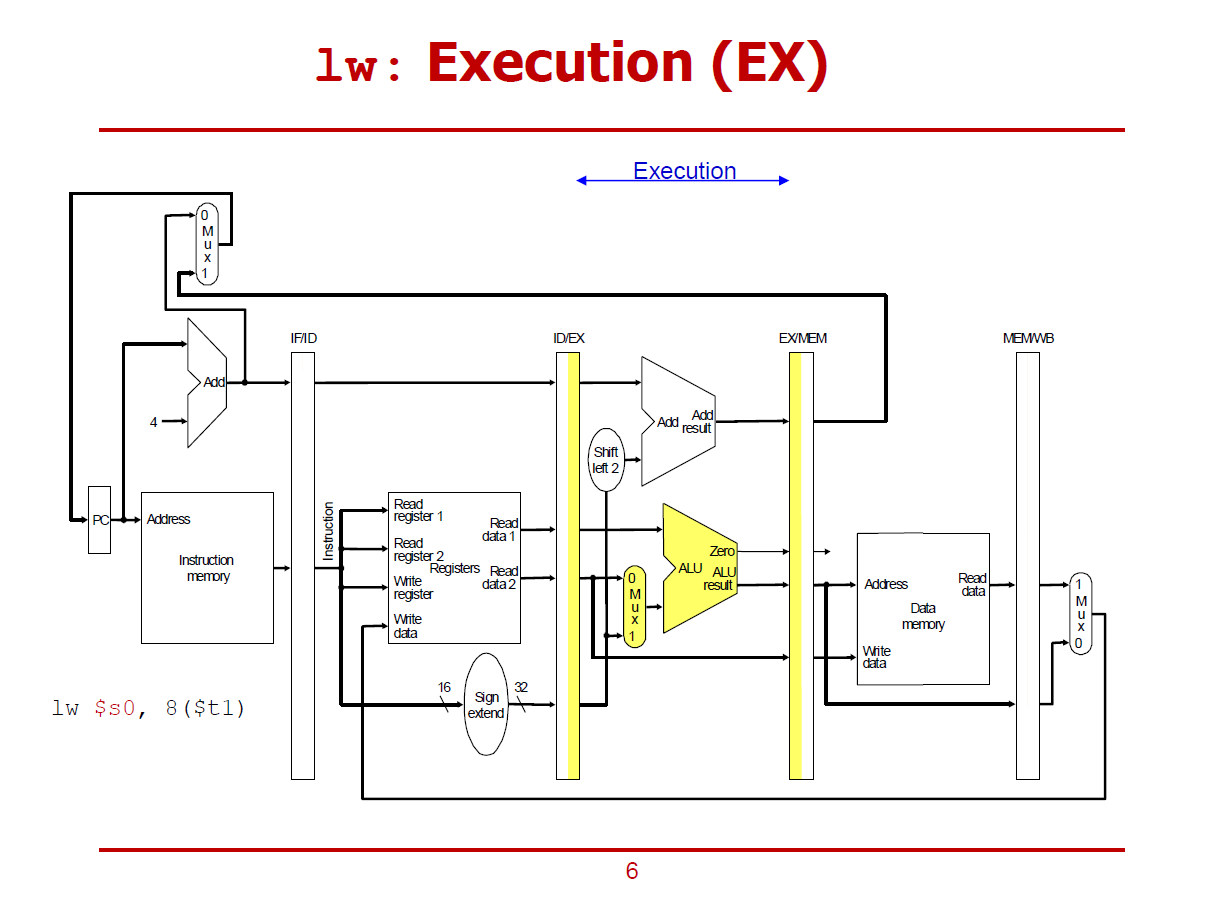

- Clock 신호가 들어오면, ID/EX 파이프라인 레지스터로부터 PC+4, 레지스터 출력, Sign-extend로 부터의 출력값을 넘겨 받게된다.

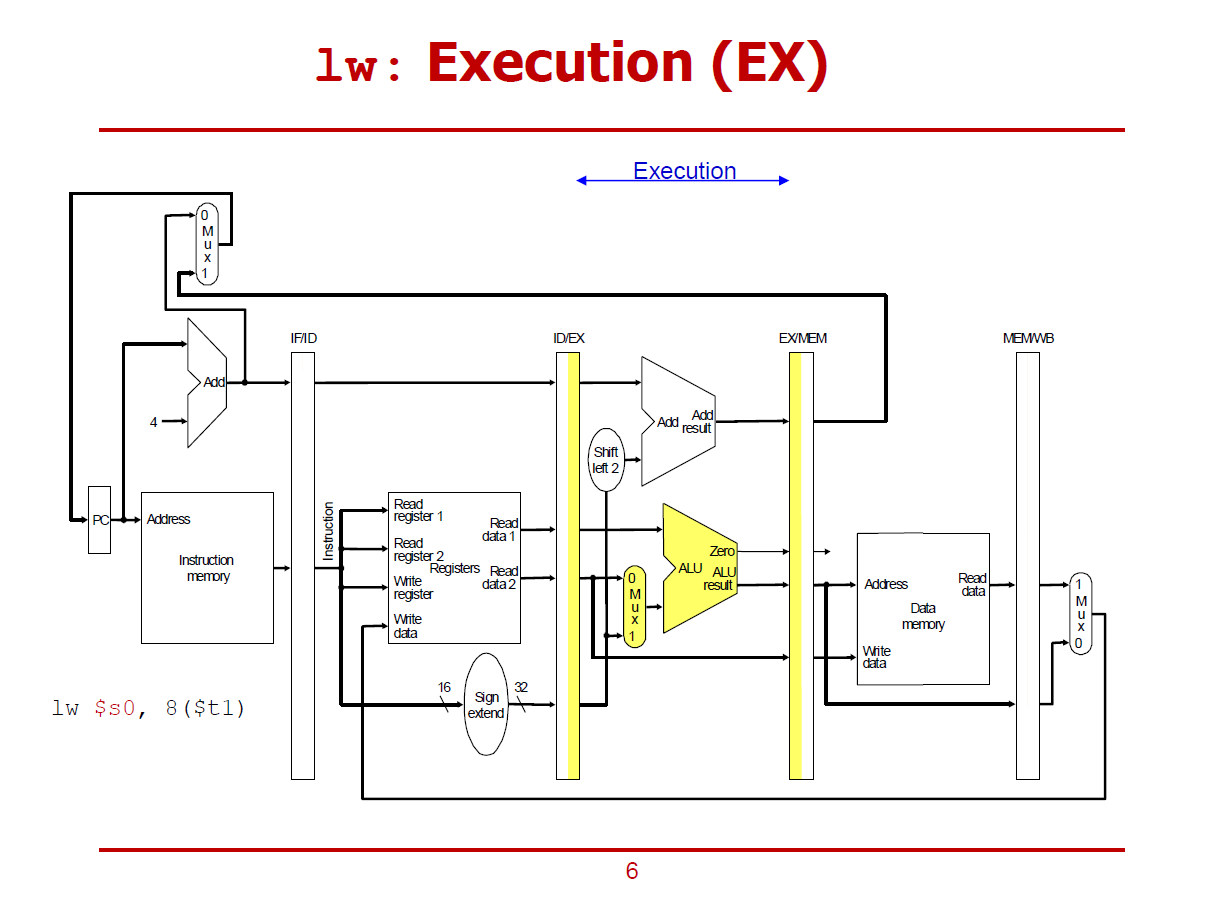

- 접근하고자 하는 Data Memory의 주솟값을 계산하는 Stage이다.

- 레지스터로부터 전달된 Base 주솟값과 Sign-Extension된 Offset값을 ALU가 더한다.(이 결과는 ALU result로써 출력된다.)

- ALU 위의 Adder는 분기 명령어를 처리할 때 분기 주소를 계산하기 위해 사용되는 Resource이기 때문에, \(\texttt{lw}\) 명령어를 처리할 때는 쓰이지 않는다.

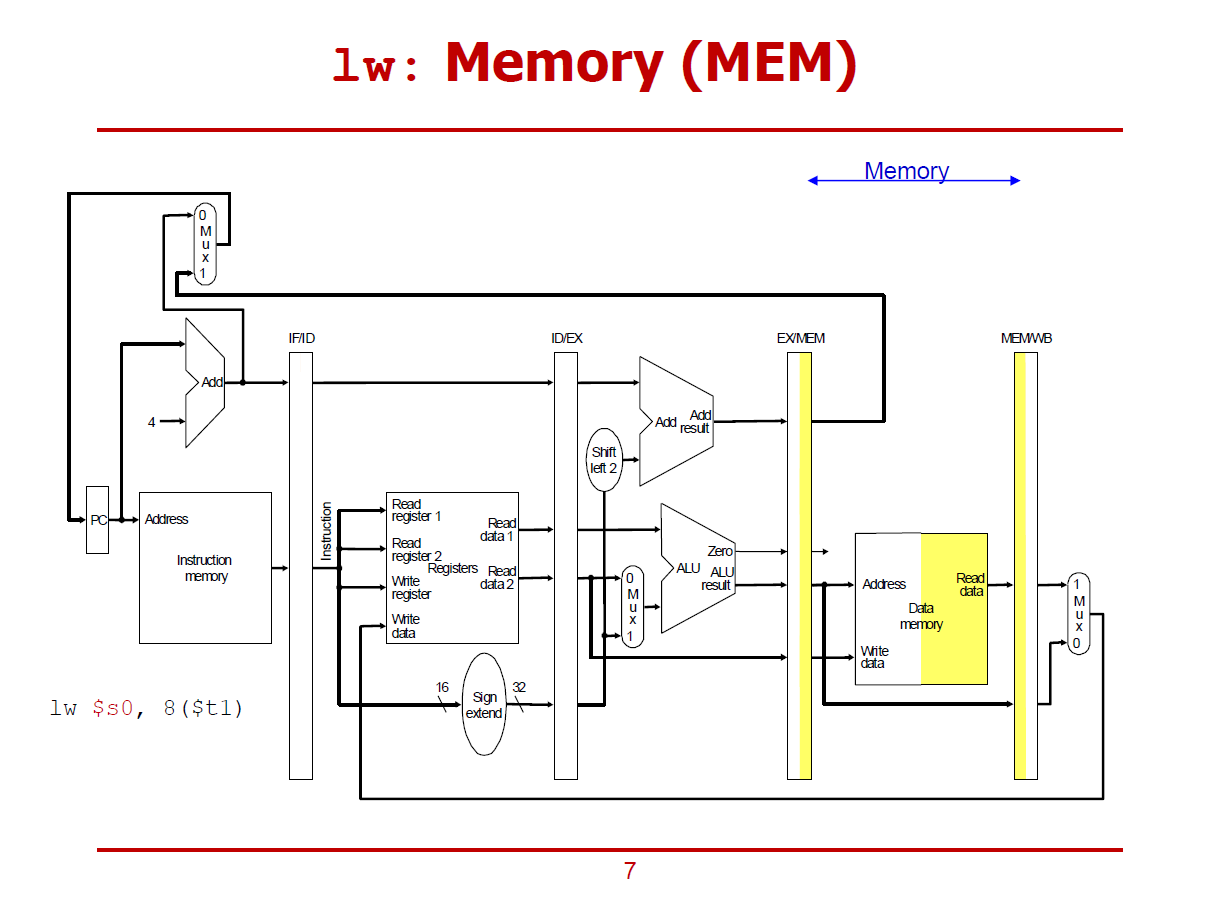

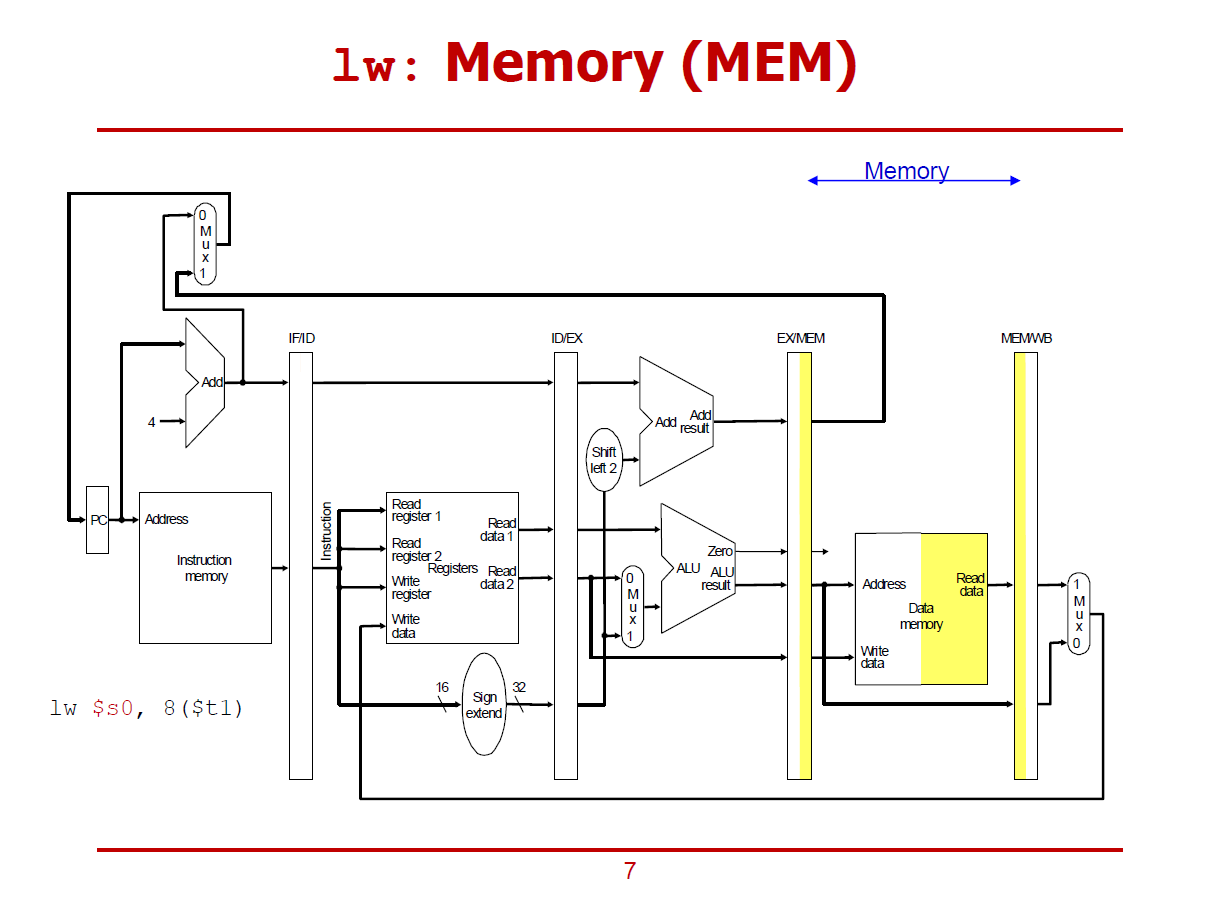

- Clock 신호가 들어오면, EX/MEM 파이프라인 레지스터로부터 ALU result(메모리 주솟값)를 넘겨 받게된다.

- ALU result를 이용해 Data Memory 읽기 동작을 수행한다.

- Data Memory의 ALU result에 해당되는 위치에 저장된 값을 MEM/WB 파이프라인 레지스터에 넘긴다.

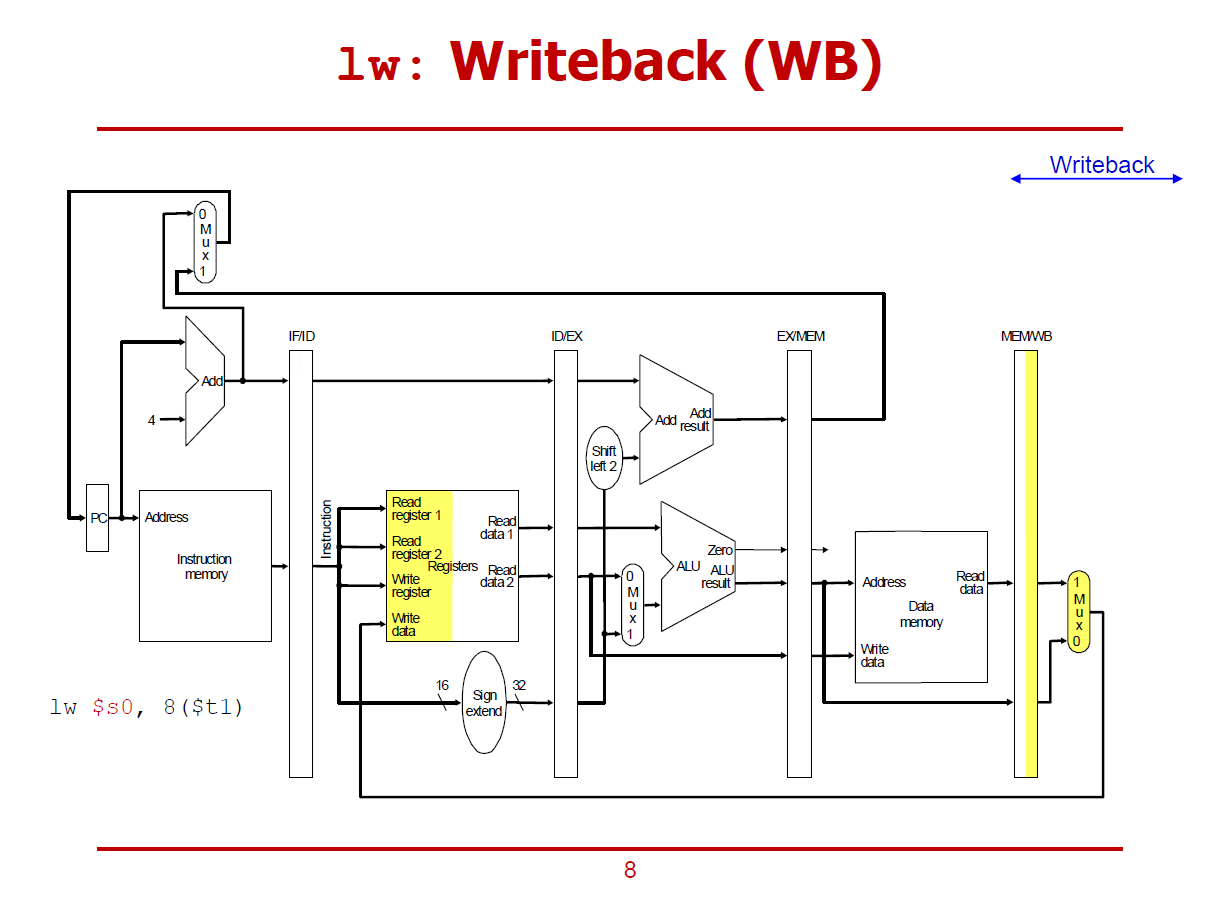

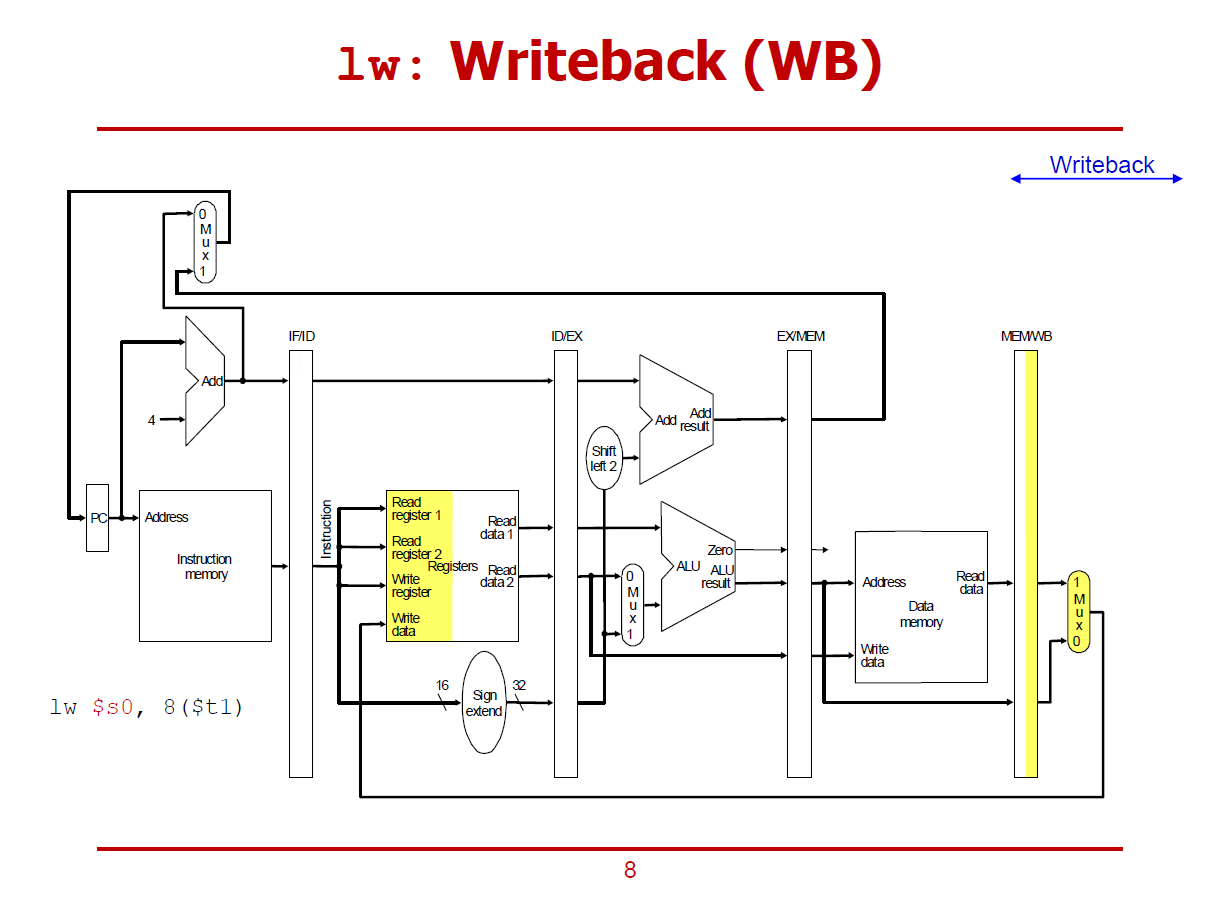

- Clock 신호가 들어오면, MEM/WB 파이프라인 레지스터로부터 Data Memory의 특정 위치에 저장된 값을 넘겨받게 된다.

- 넘겨받은 Read Data는 MUX를 거쳐서 레지스터의 특정 위치*(\(\texttt{\$s0}\) 레지스터)에 저장된다.

* 여기서 특정위치는 레지스터의 Write register에 해당되는데, 이 레지스터의 특정 위치가 WB Stage에서 입력되어야 하는데, ID Stage에서 Register 파일 읽기 동작을 수행할 때 입력되어 버려졌다.

즉, 위 그림에는 오류가 있다. (Write register 값이 WB Stage가 아닌, ID Stage에 입력되어 버렸다는 점)

※ 위 그림은 Data Memory로 부터 Load한 값을 다른 명령어의 Destination Field가 가리키는 레지스터에 저장하게 될 수도 있다. (사실, 어떤 오류가 생길 지 모른다.)

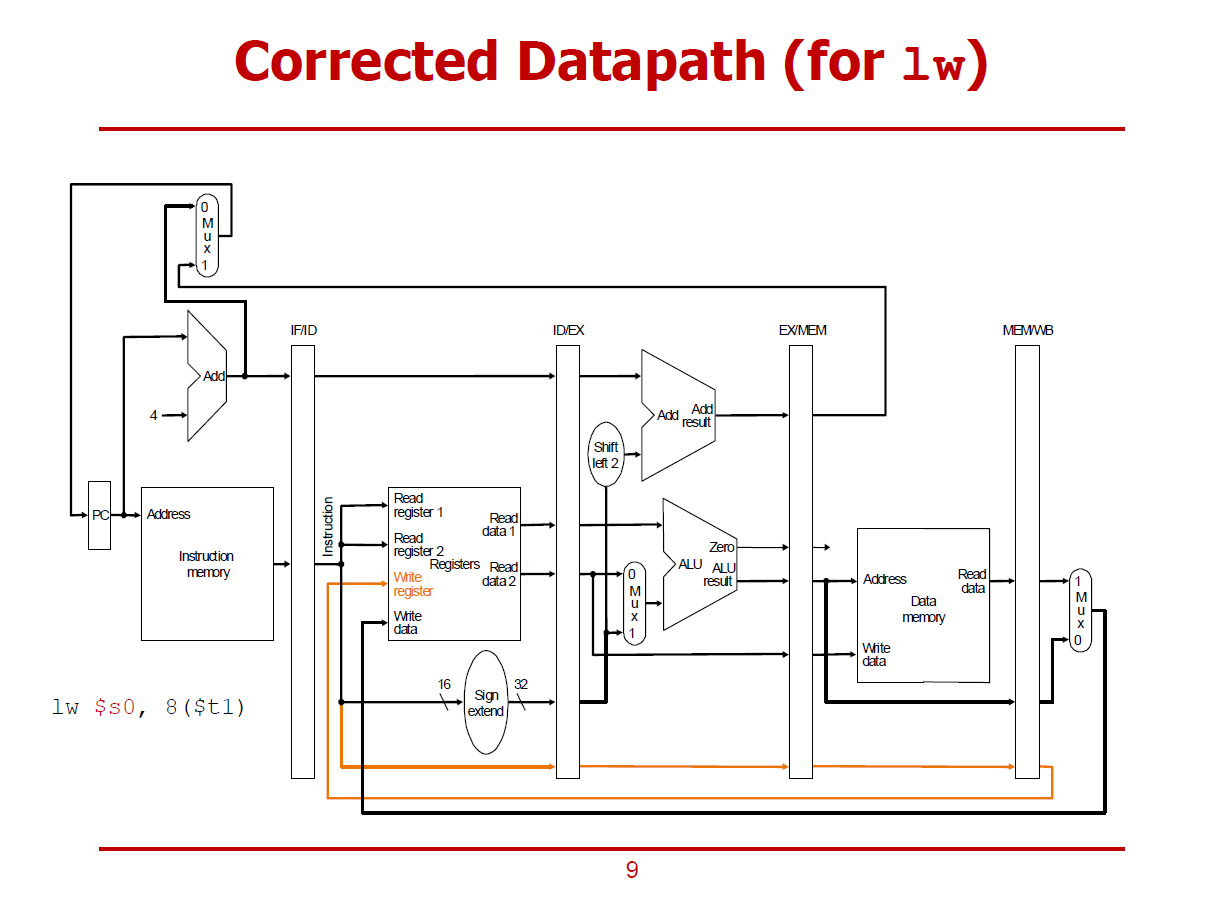

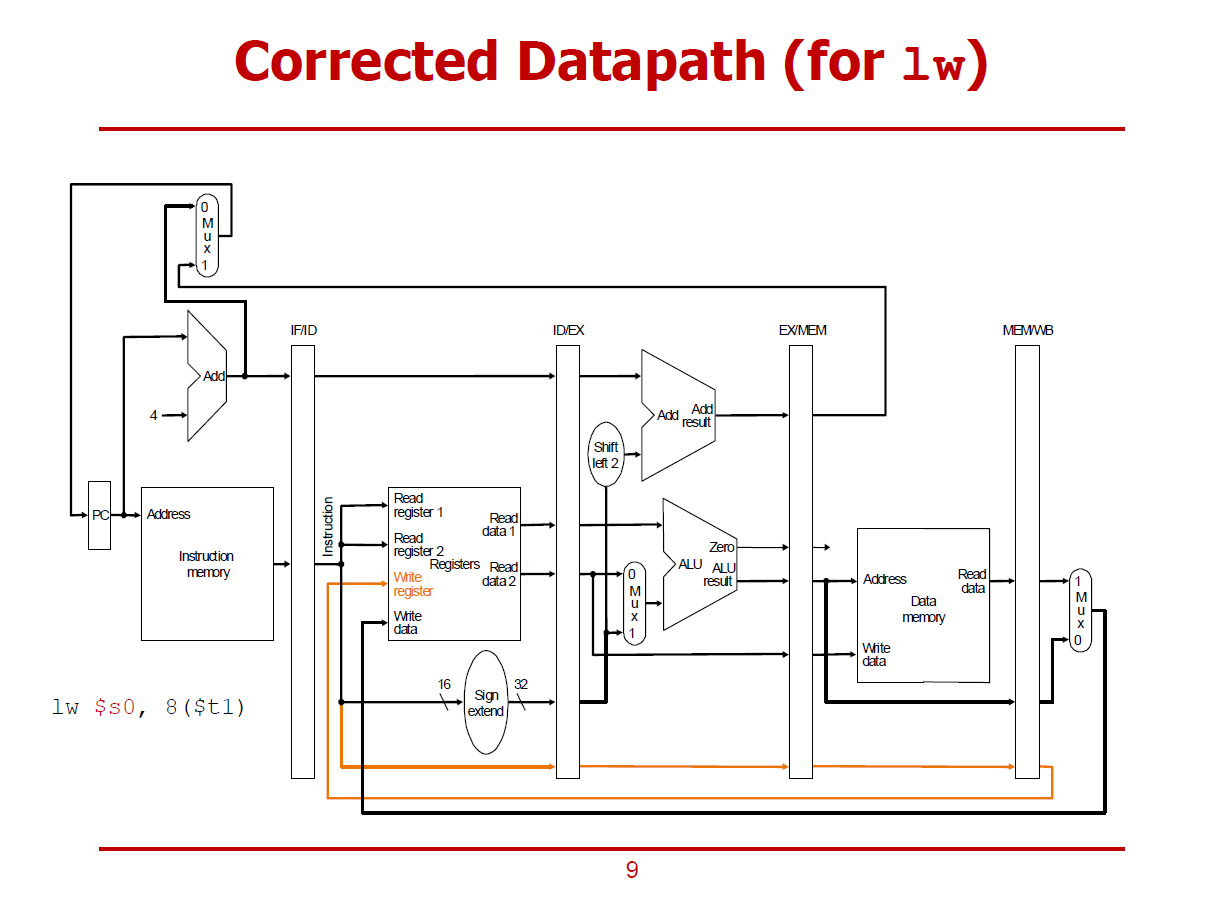

- 위 그림의 오렌지 색 Path처럼 Write register에 해당되는 값(Destination Field)이 WB Stage까지 유보되어야 정상적으로 메모리에서 Load한 값을 레지스터 파일에 저장할 수 있다.

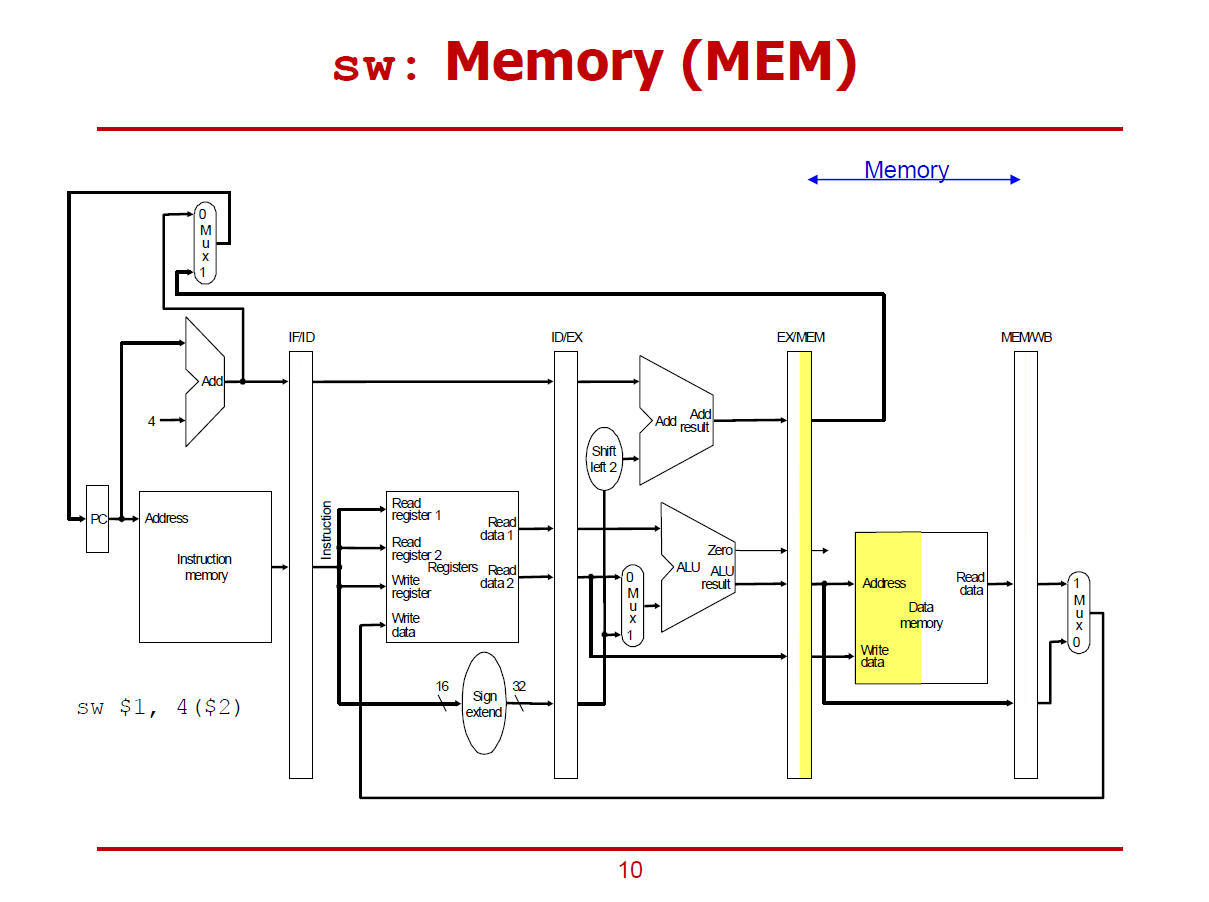

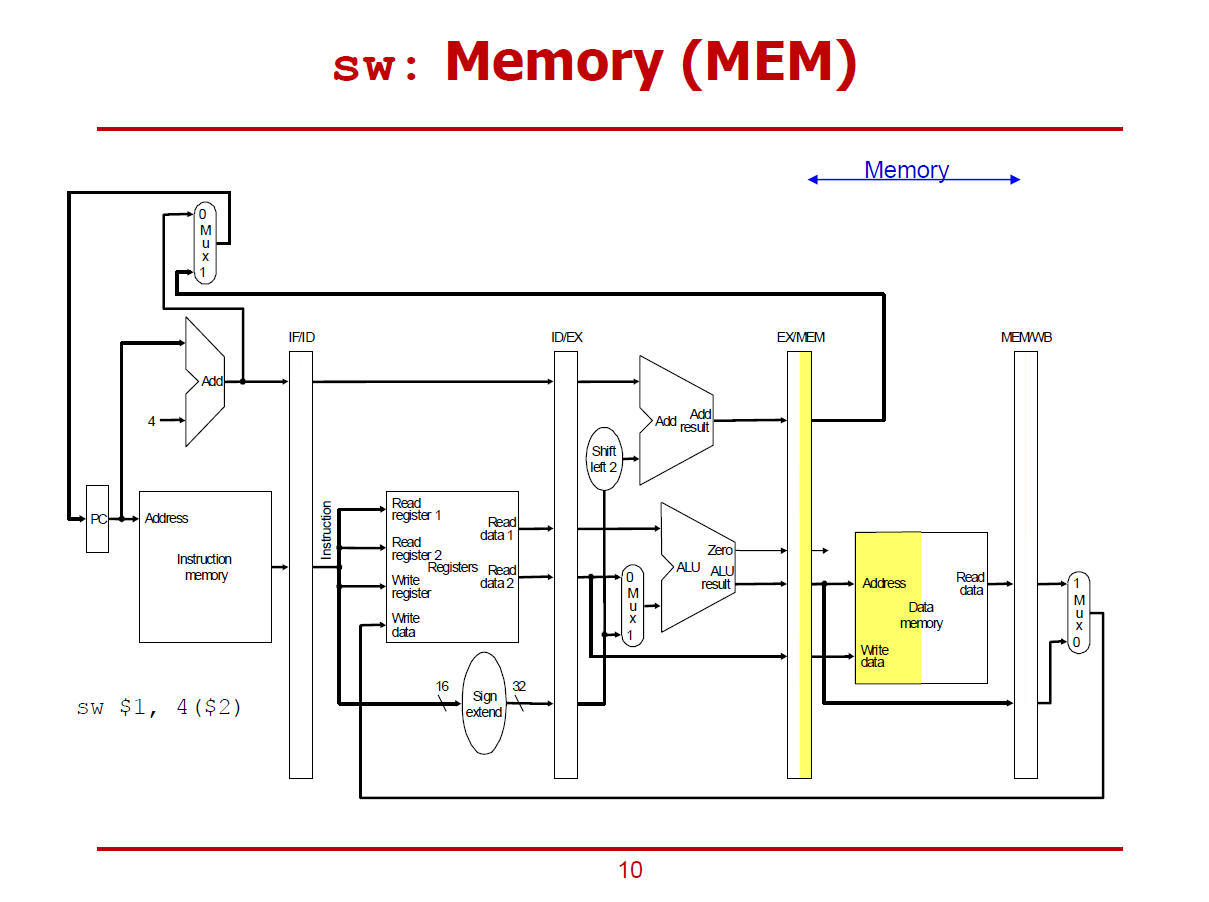

- \(\texttt{lw}\)와 달리, \(\texttt{sw}\) 명령어가 처리될 때의 차이점을 다룬다.

- MEM Stage에서의 \(\texttt{sw}\) 명령어는 \(\texttt{lw}\) 명령어와 달리, Data Memory 쓰기 동작을 수행한다.

- ID Stage에서 레지스터 파일 접근을 통해 읽은 데이터를 각각의 Stage들로부터 넘겨받아 Write Data 포트에 입력하게 된다.

- \(\texttt{sw}\) 명령어의 주소 계산(Base + Offset)은 \(\texttt{lw}\) 와 비슷하게 수행된다.

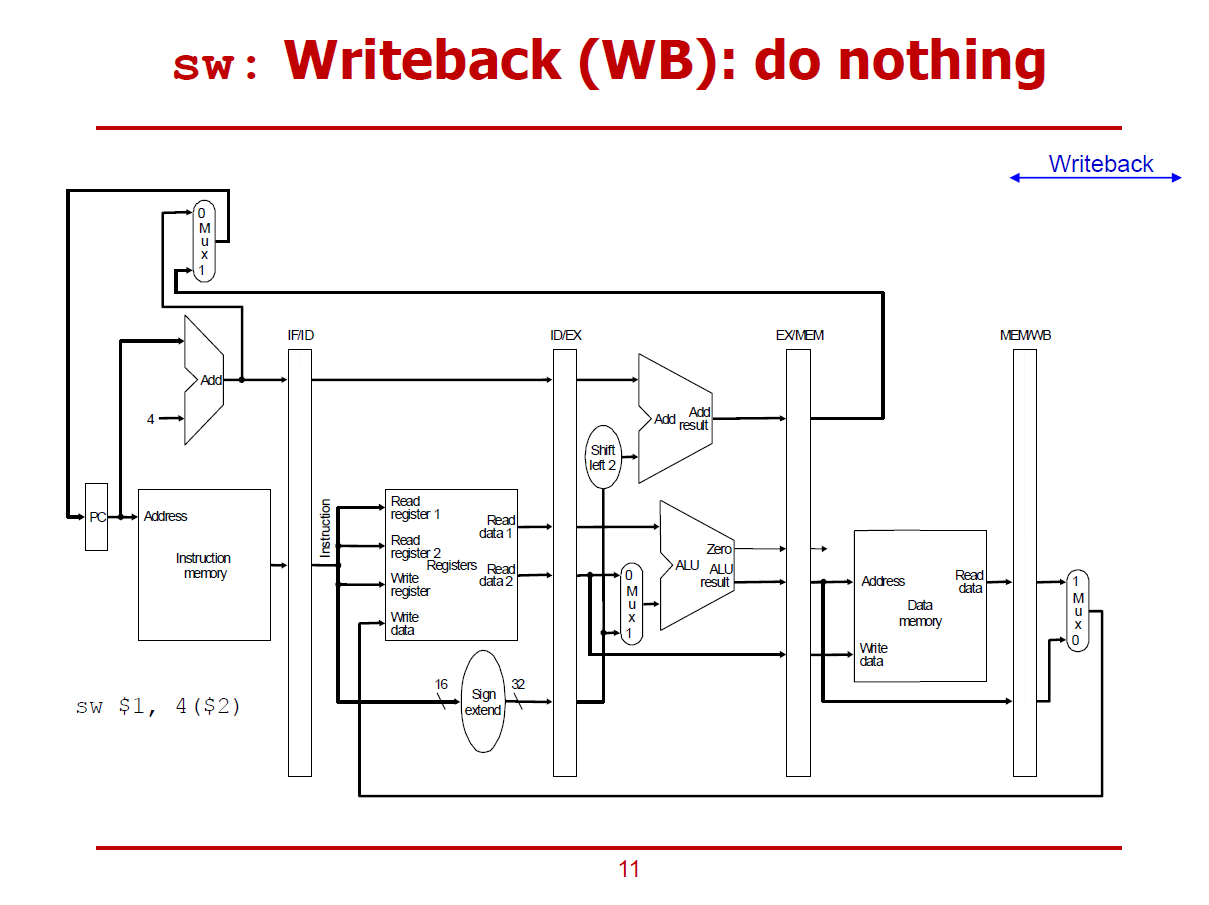

- \(\texttt{sw}\) 명령어는 WB Stage에서는 아무런 연산도 수행하지 않는다.

- 값을 메모리에 저장하는 연산이지, 레지스터에 저장하는 연산이 아니기 때문이다.

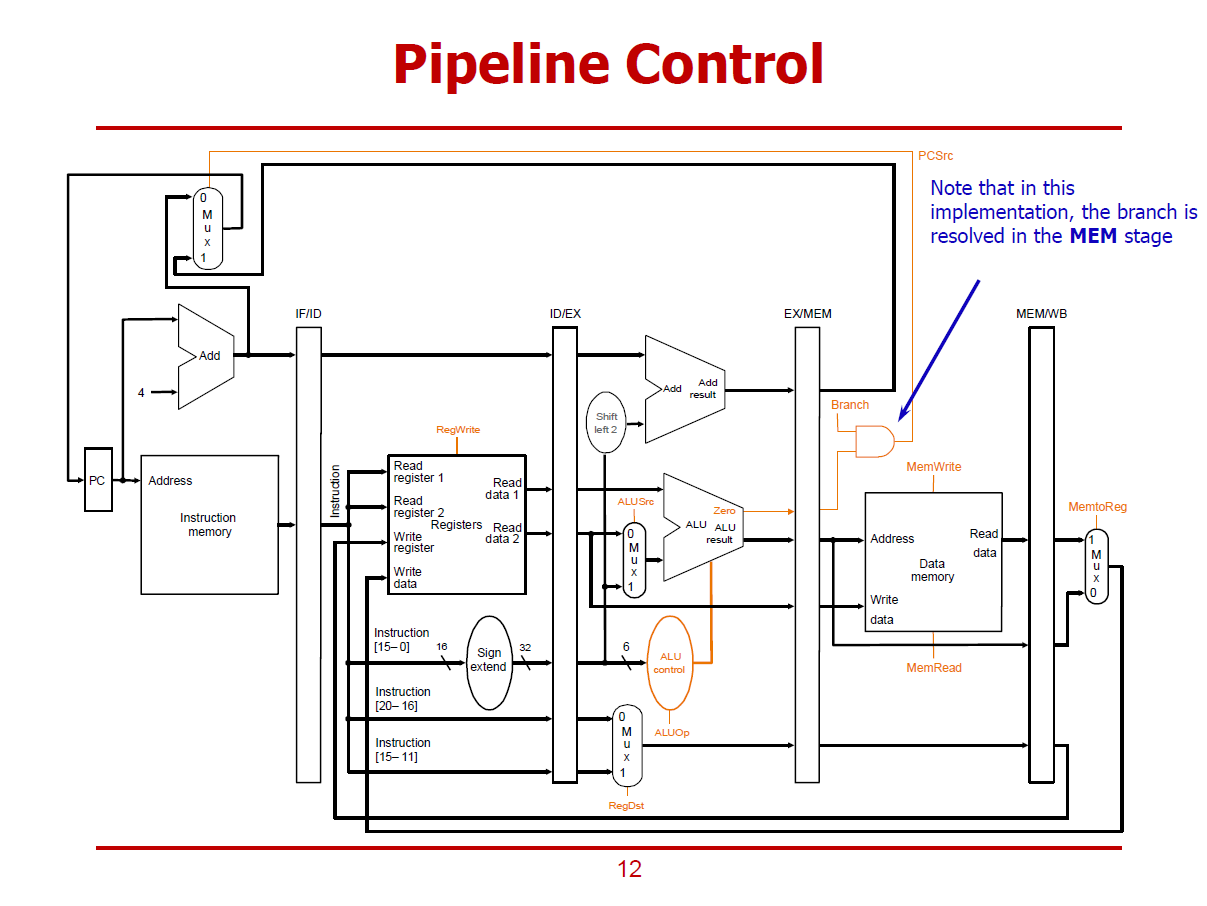

- Control Logic까지 반영하여 생각해본다.

- Control Logic은 대부분 MUX를 제어하거나, 메모리 쓰기 동작을 Enable하도록 하는 의도로 설계되었다.

- 각 Control 신호들은 자신들이 위치한 Stage에서 활용되어진다.

※ 단, RegWrite 신호는 실제로 ID Stage가 아닌, WB Stage에서 활용된다.

※ Branch 신호와 Zero 신호를 AND 연산한 PCSrc 또한, MEM Stage에서 활용하는 것으로 약속한다. (구현 방법에 따라 달라질 수 있다.)

- IF Stage에서는 어떠한 Control 신호도 필요없음을 확인할 수 있다.

- ID Stage에서도 어떠한 Control 신호도 필요없음을 확인할 수 있다. (RegWrite은 WB Stage에서 활용된다.)

- Control 신호들은 앞서 다뤘던 Single Cycle MIPS와 기능적인 측면에서는 동일하다.

- 각각의 Control 신호들이 어느 Stage에서 사용되는지를 나타낸 것이며, 생성 시기와는 무관하다.

1. IF Stage

- 명령어를 무조건 Fetch하고, PC도 항상 4만큼 증가시키기 때문에 별도의 Control 신호를 필요로하지 않는다.

2. ID Stage

- 넘겨받은 명령어를 해석하고, 레지스터 파일에 접근, Immediate 값을 Extension 하는 작업만 수행하기 때문에 별도의 Control 신호를 필요로하지 않는다.

- 단, Control 신호를 생성할 수 있는 Stage이다. (명령어가 해석되는 단계이기 때문이다.)

3. EX Stage

- RegDst

- ALUop[1:0]

- ALUSrc

4. MEM Stage

- Branch

- MemRead

- MemWrite

5. WB Stage

- MemtoReg

- RegWrite

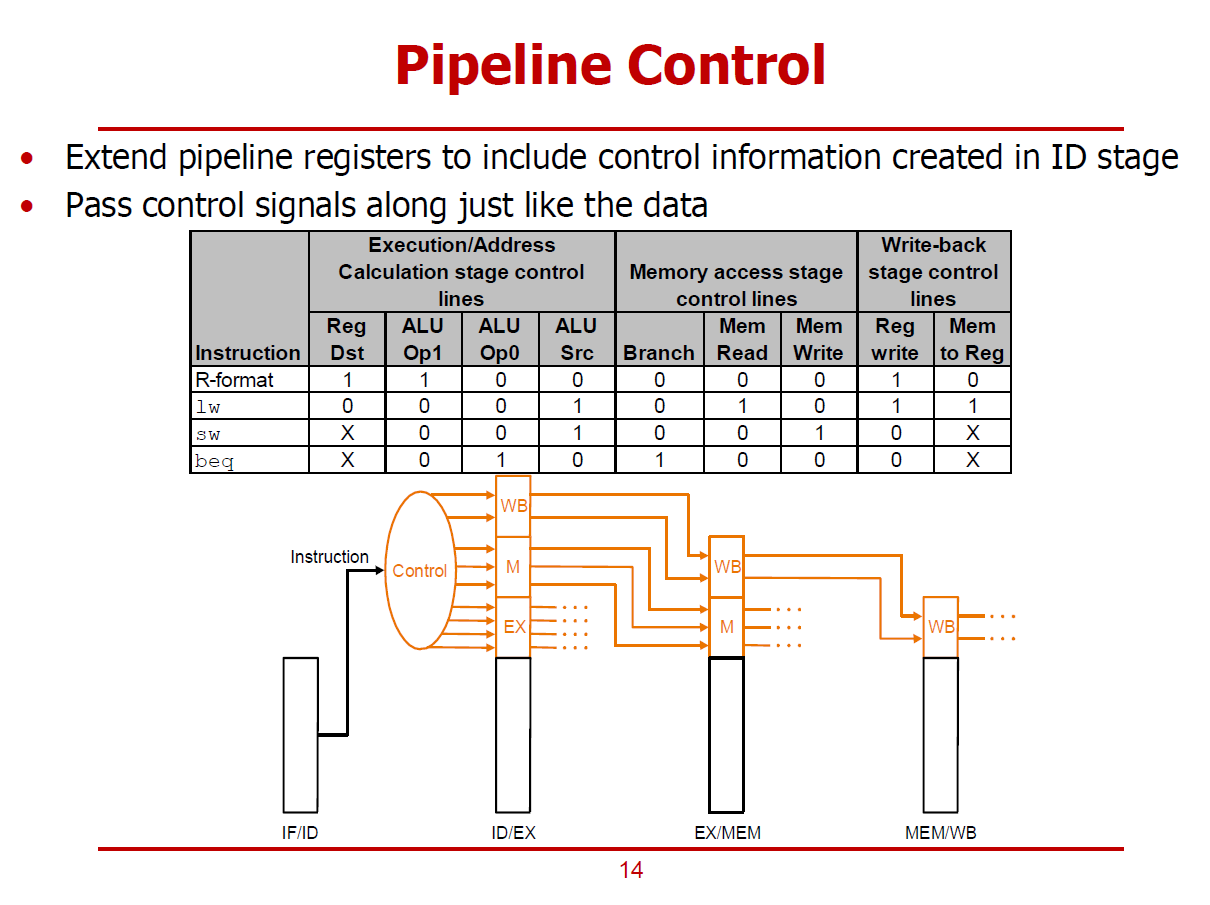

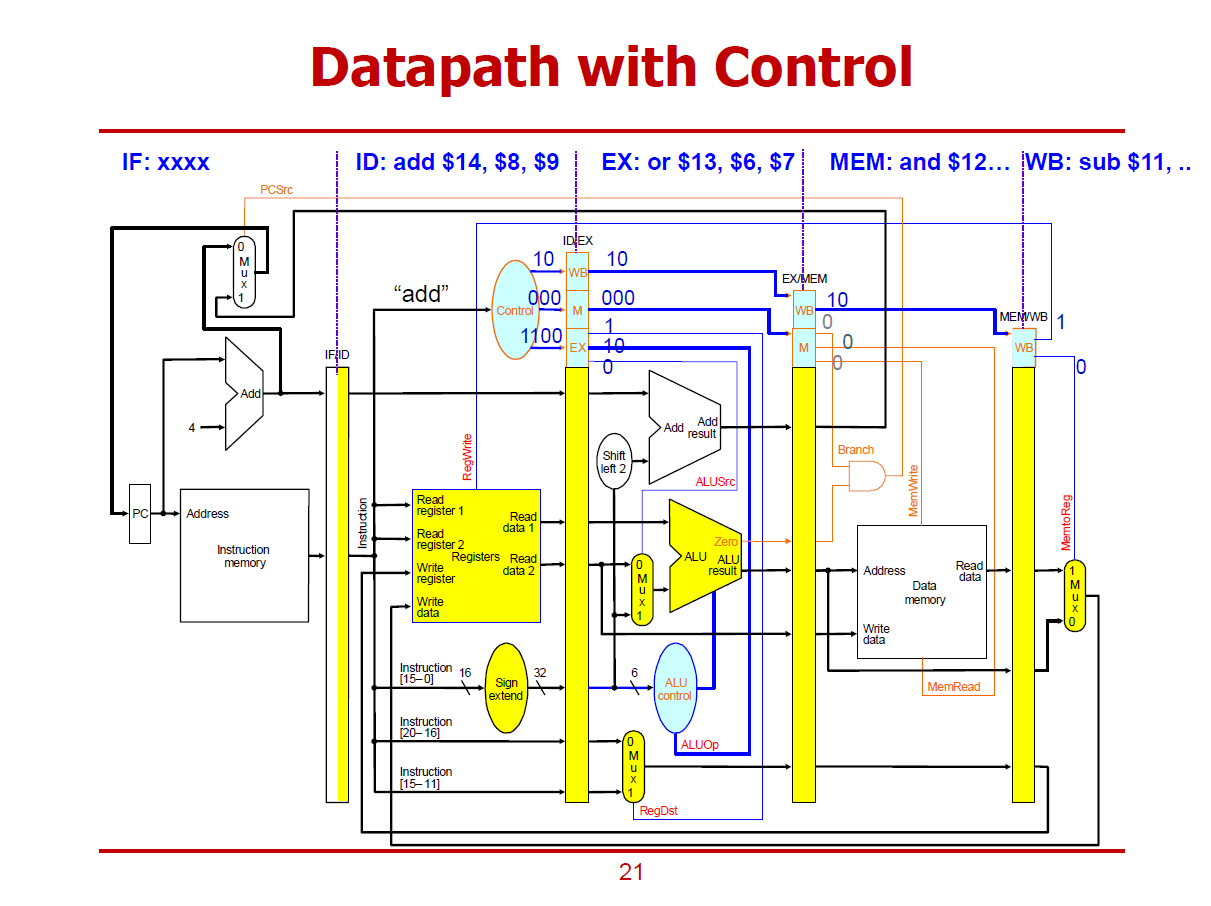

- Stage별로 다르게 사용되는 Control 신호들을 어떻게 생성하고 유지할 것인지에 대한 내용이다.

- 9개의 Control 신호가(ALUop[1:0]은 2개의 신호로 간주) 하나의 표로 정리되어 있다.

- 9개의 Control 신호들은 명령어의 OP-Code와 Funct Code를 통해 ID Stage에서 계산된다.

- 만들어진 Control 신호들은 ID Stage에서 사용되지 않고, 파이프라인 레지스터로 이동되어 알맞은 Stage에서 활용된다.

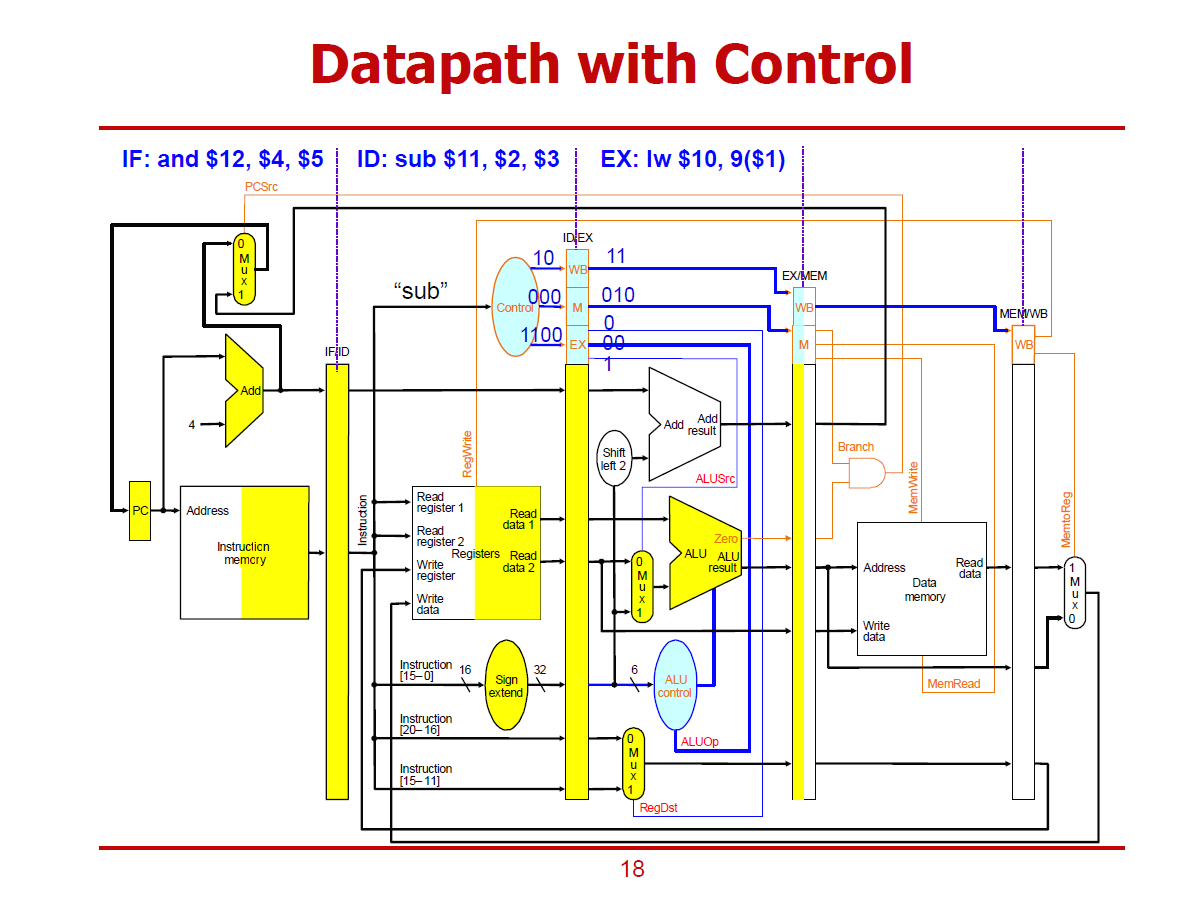

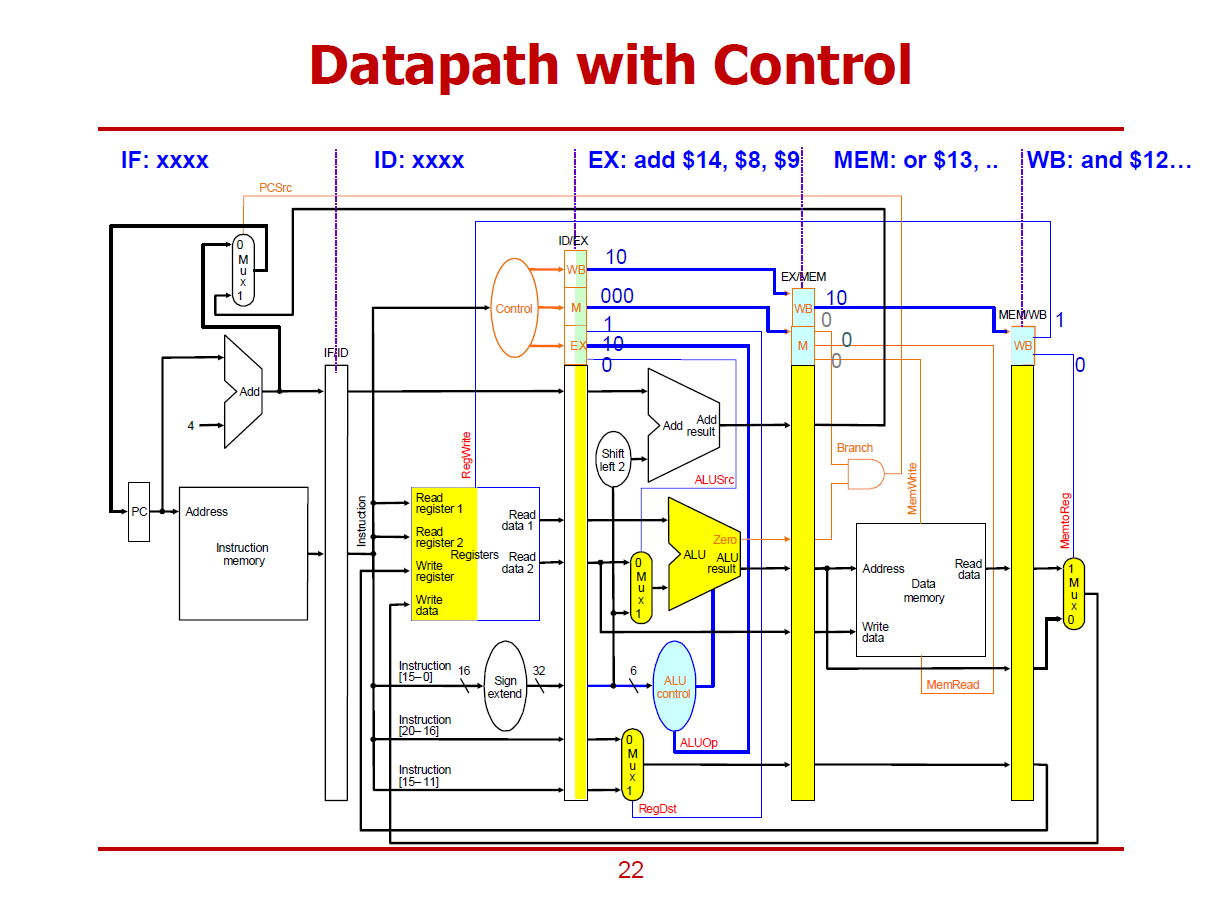

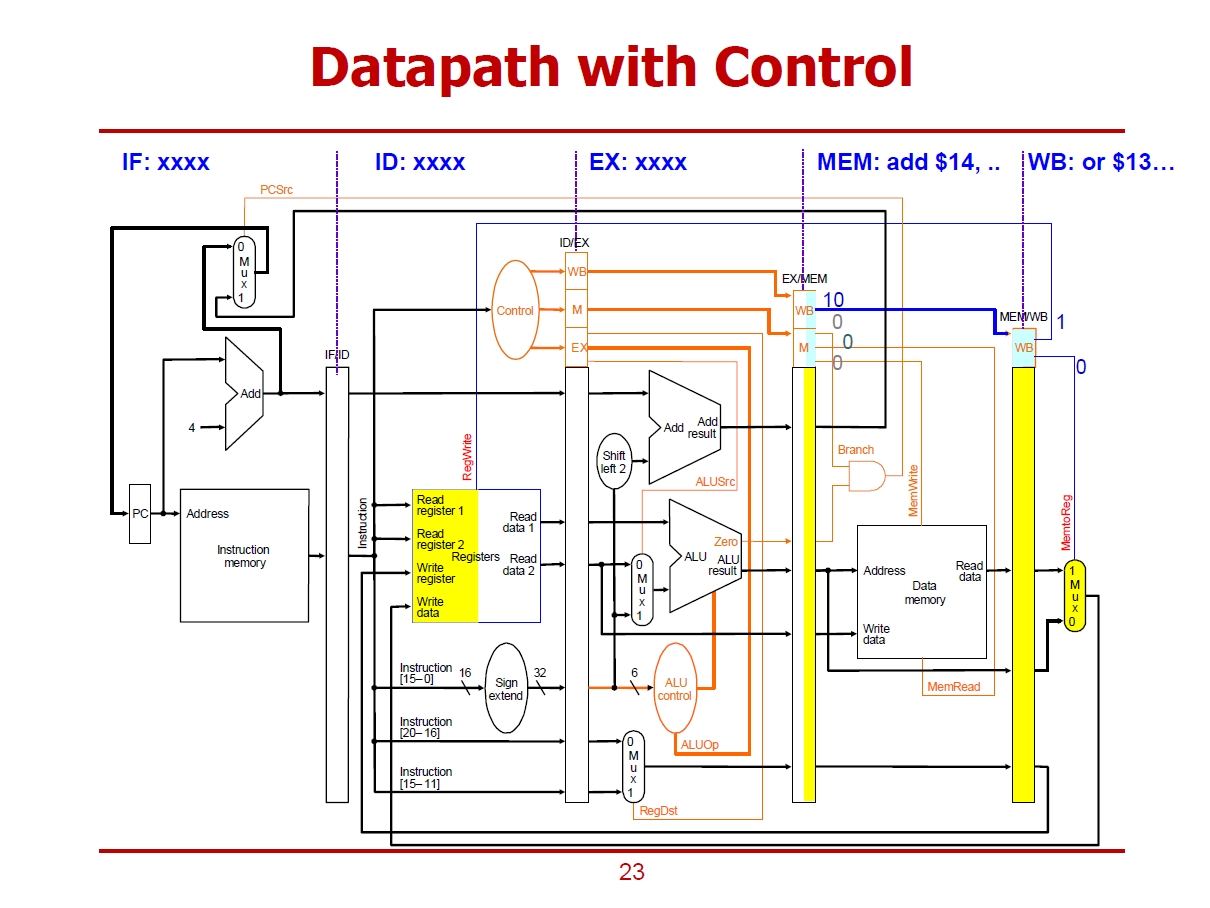

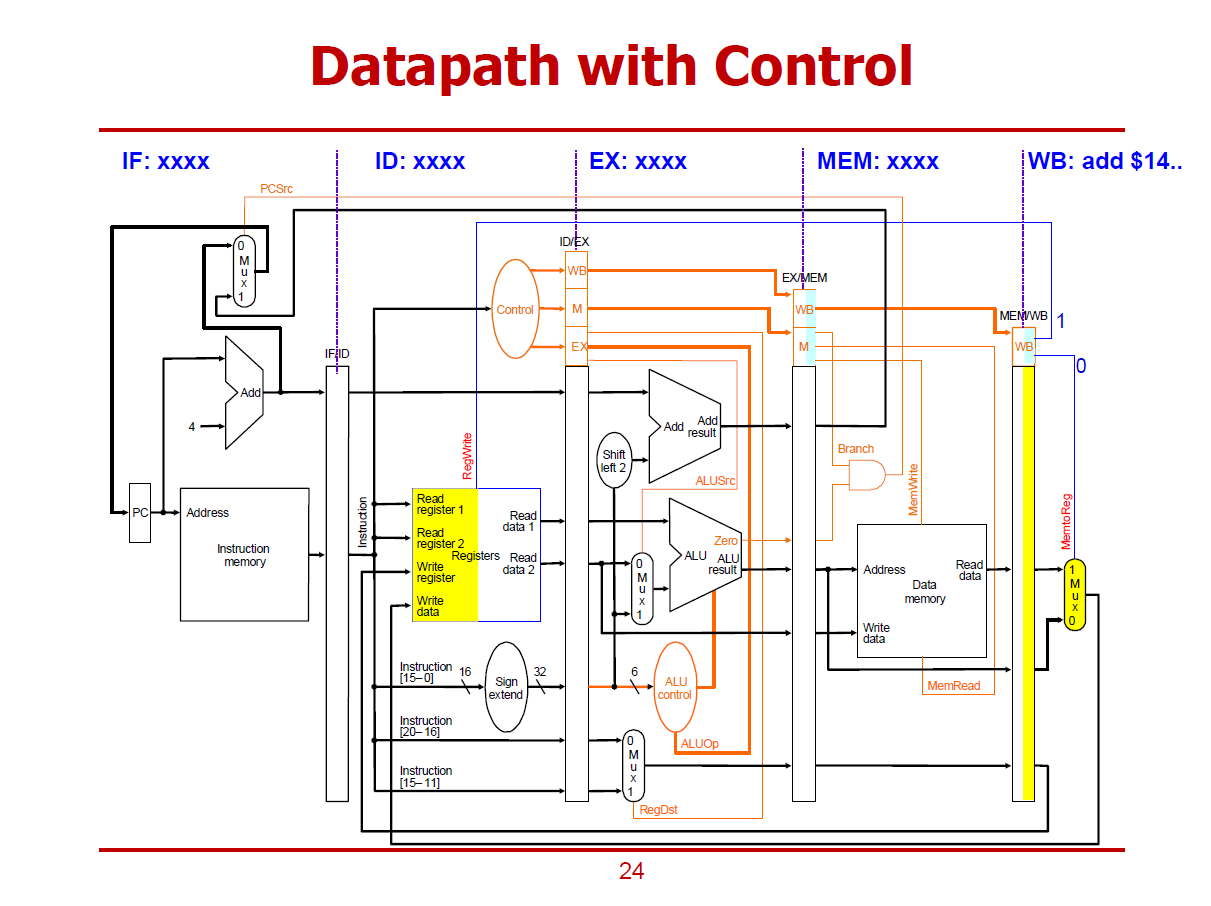

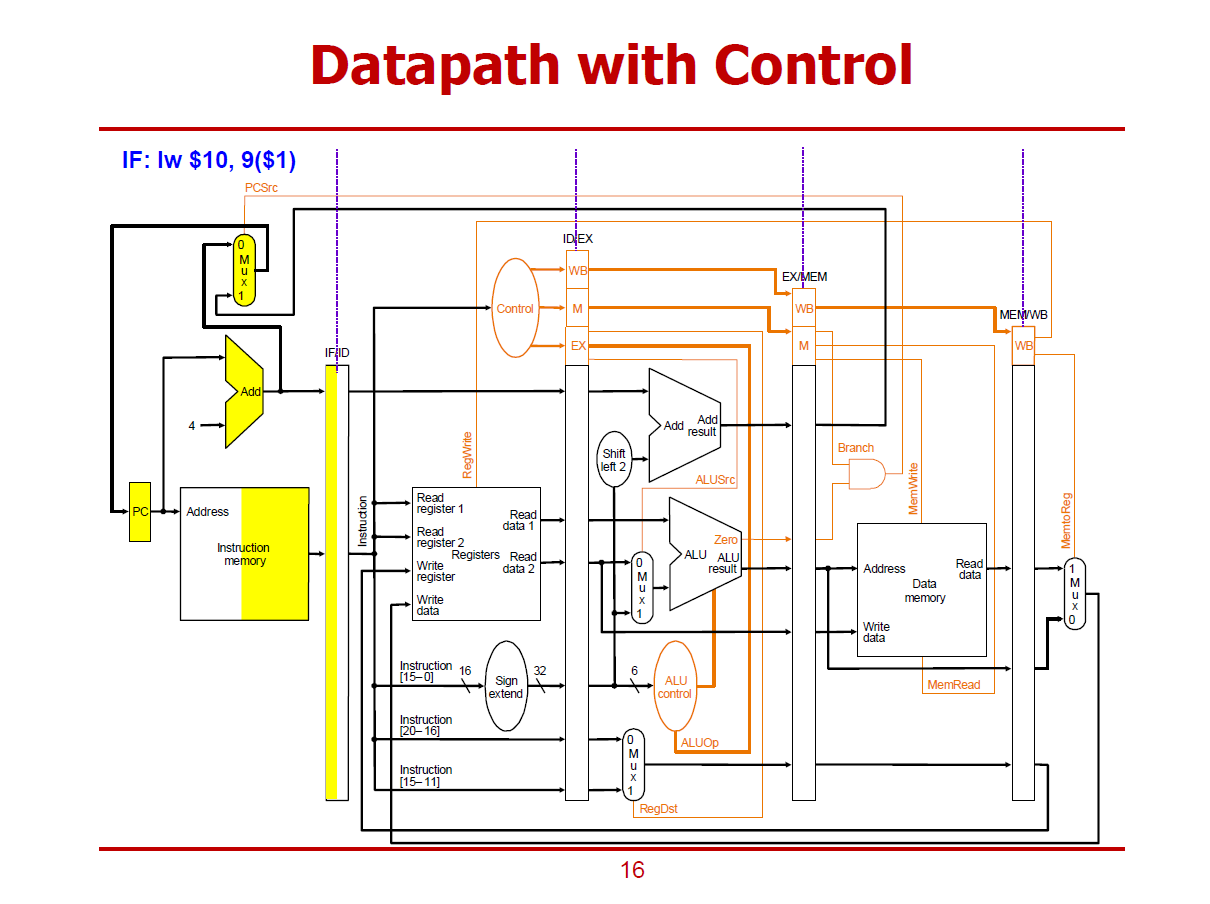

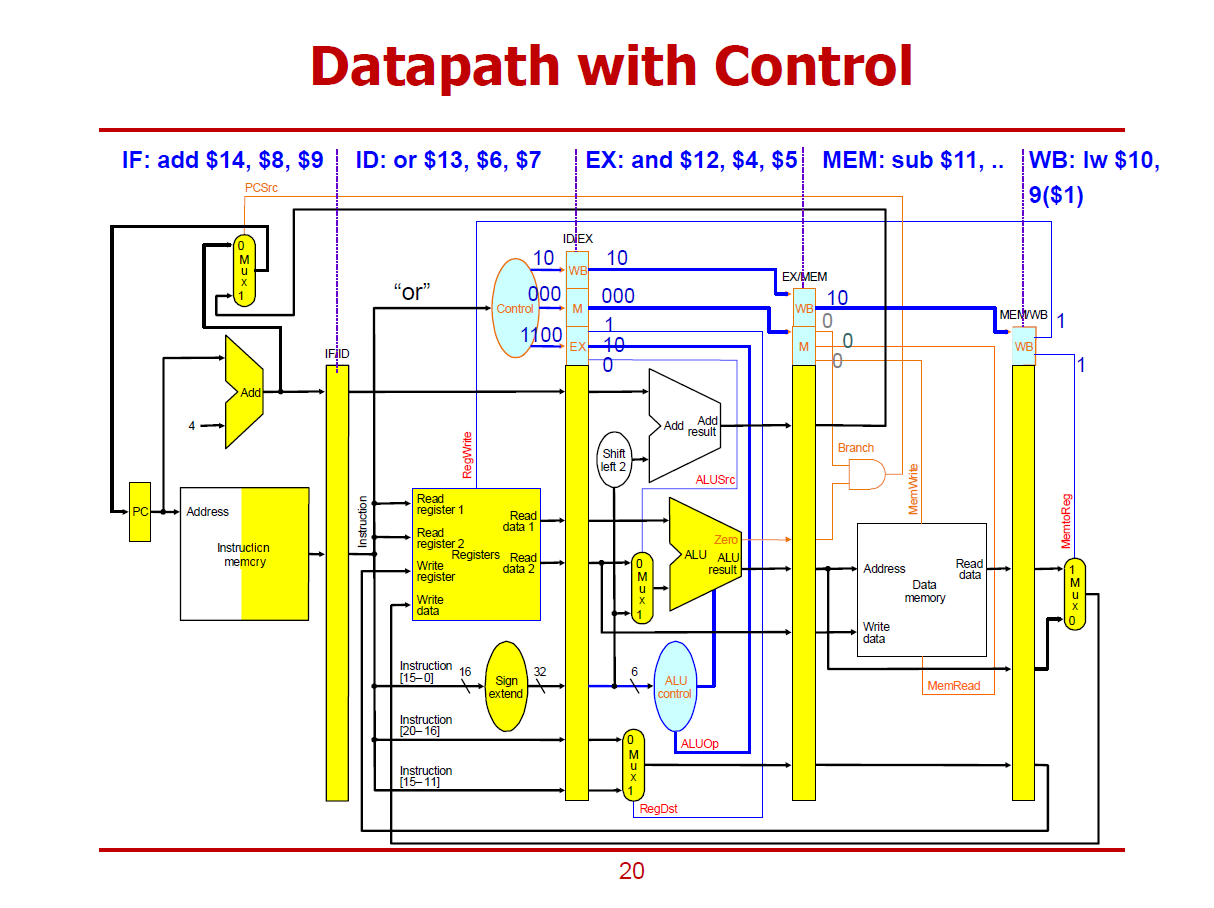

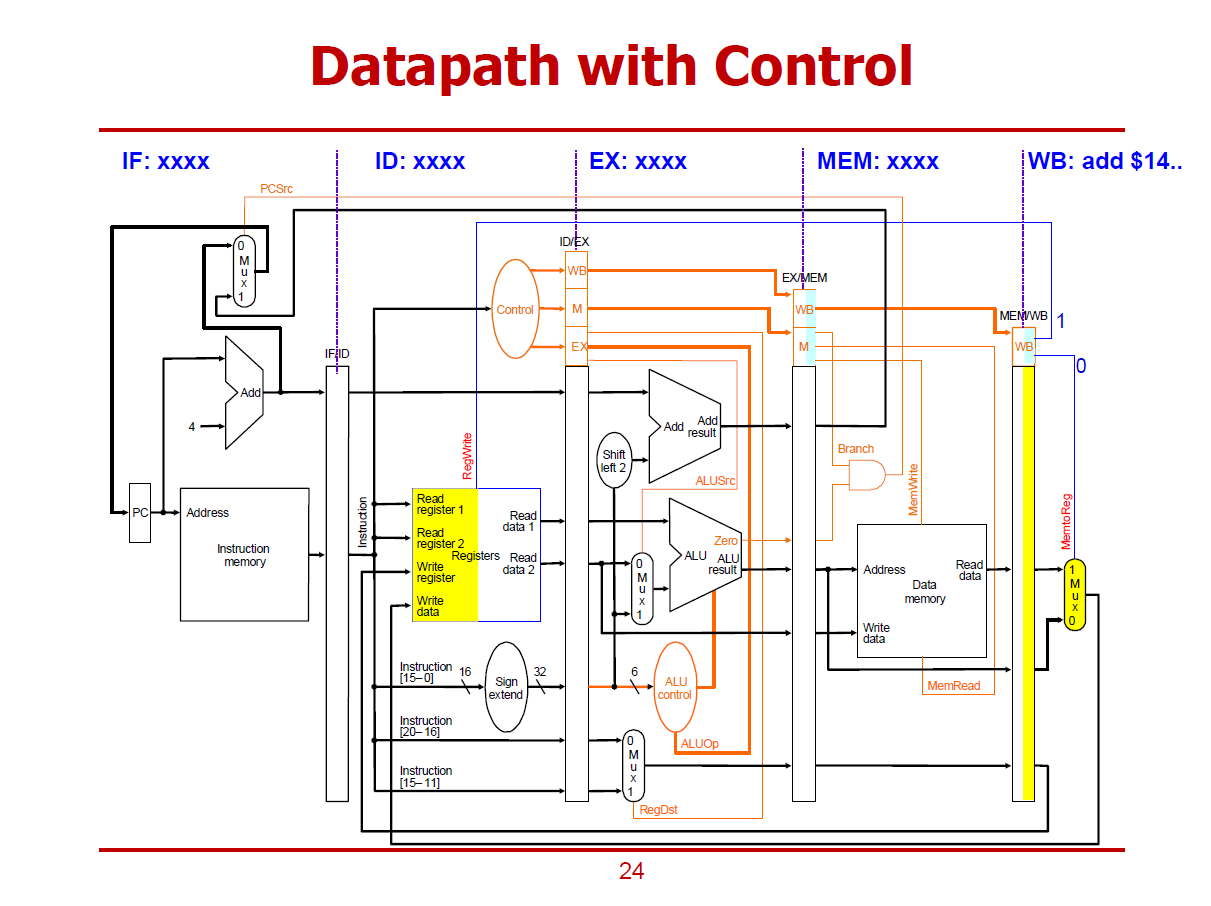

- Datapath와 Control 신호들이 모두 반영된 아키텍처 그림이다.

- \(\texttt{lw}\) 명령어가 처리되는 과정에서의 Data Path와 Control 신호들을 살펴본다.

- IF Stage에서는 Control 신호를 필요로 하지 않는다.

- 오로지, Instruction Memory로부터의 Fetch와, PC값을 4만큼 증가시키기만 한다.

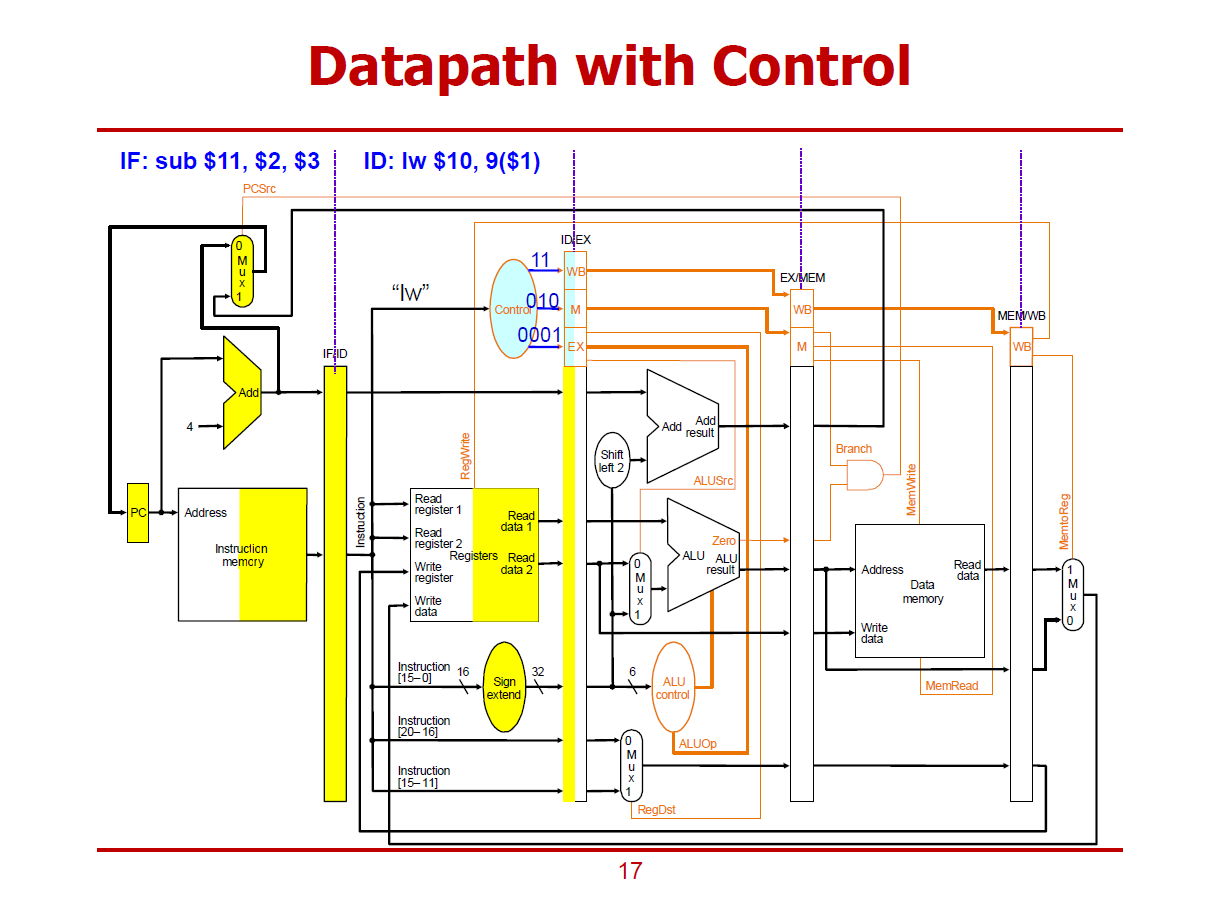

- 그 다음 클럭 사이클에서 \(\texttt{lw}\) 명령어는 ID Stage로 접어들고, \(\texttt{sub}\) 명령어가 IF Stage에 들어선다.

- ID Stage에서 해석된 \(\texttt{lw}\) 명령어는 9개의 Control 신호를 만들어낸다.

- ID Stage에서 생성된 Control 신호들은 자신이 사용될 Stage로 전달되기 위해 적절한 파이프라인 레지스터로 전달된다.

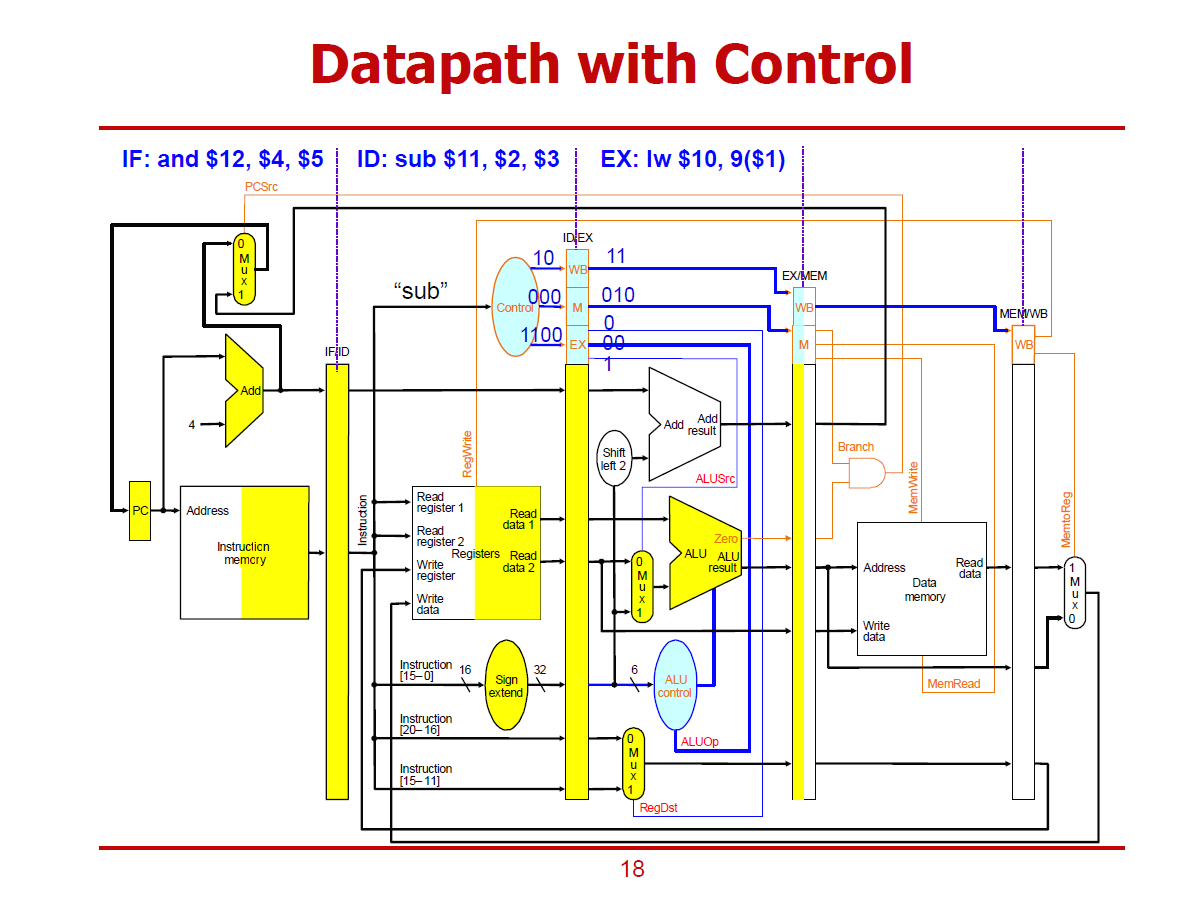

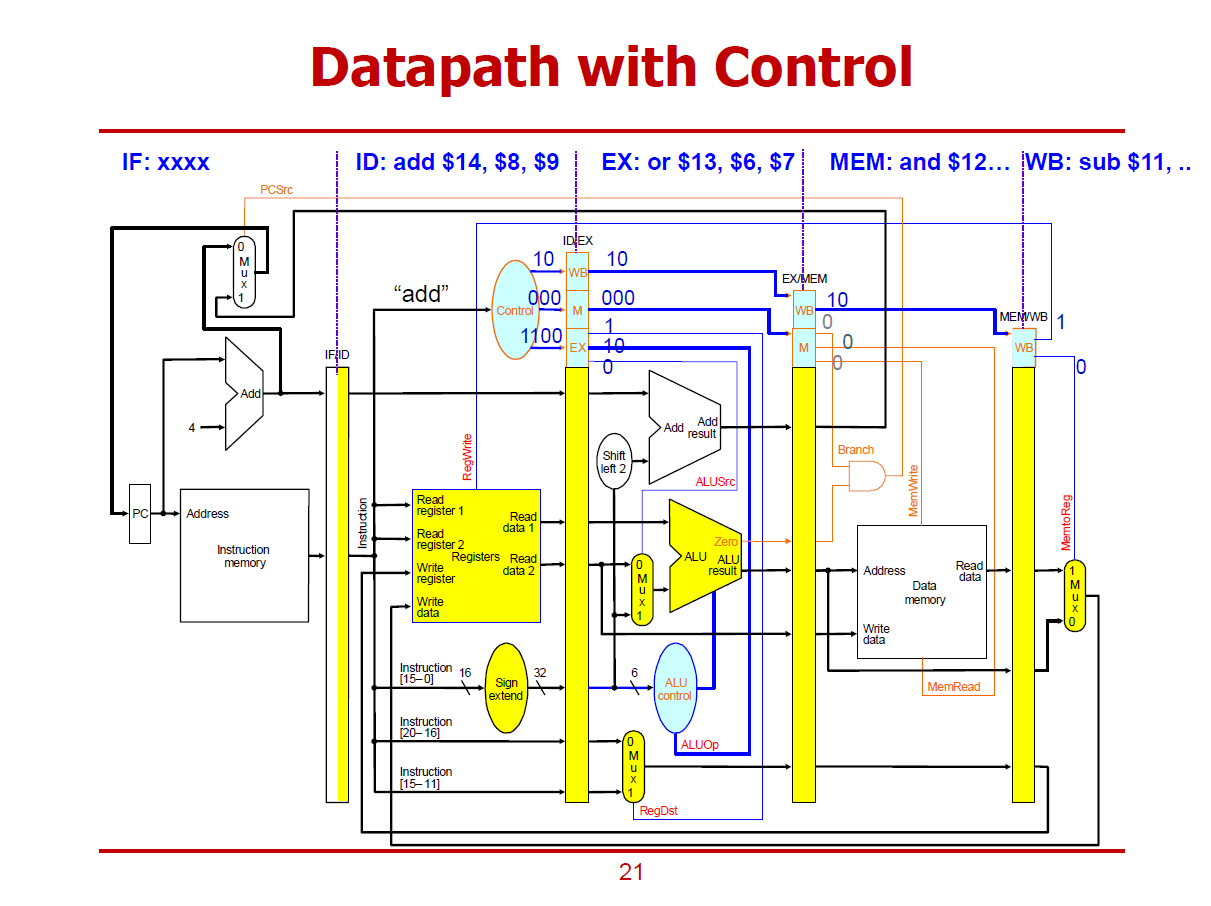

- 현재 그림에서 ID Stage에서는 \(\texttt{sub}\) 명령어에 대한 Control 신호들이 생성되고 있다.

- EX Stage에서는 이전에 생성되었던, \(\texttt{lw}\) 명령어에 대한 Control 신호들이 사용되거나 다음 Stage로 넘겨지고 있다.

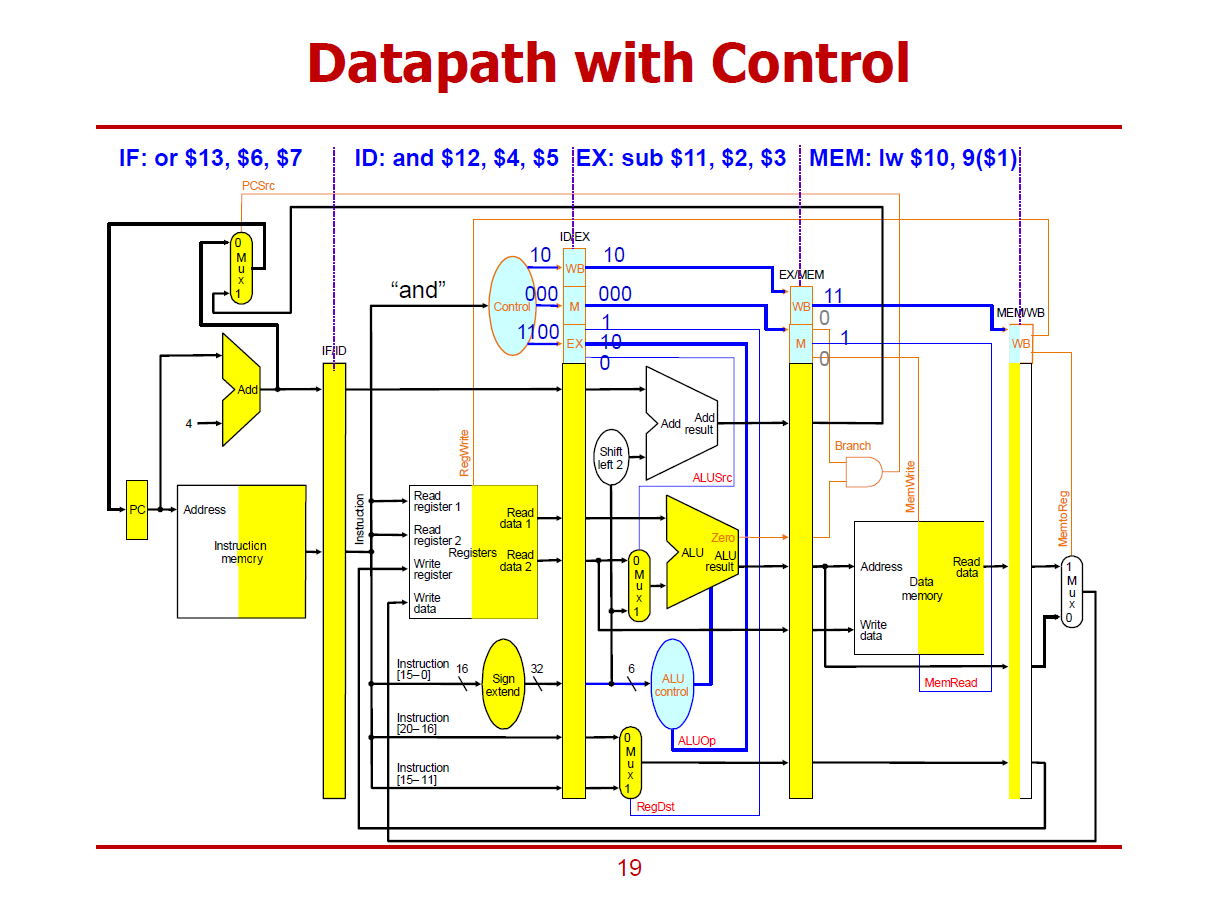

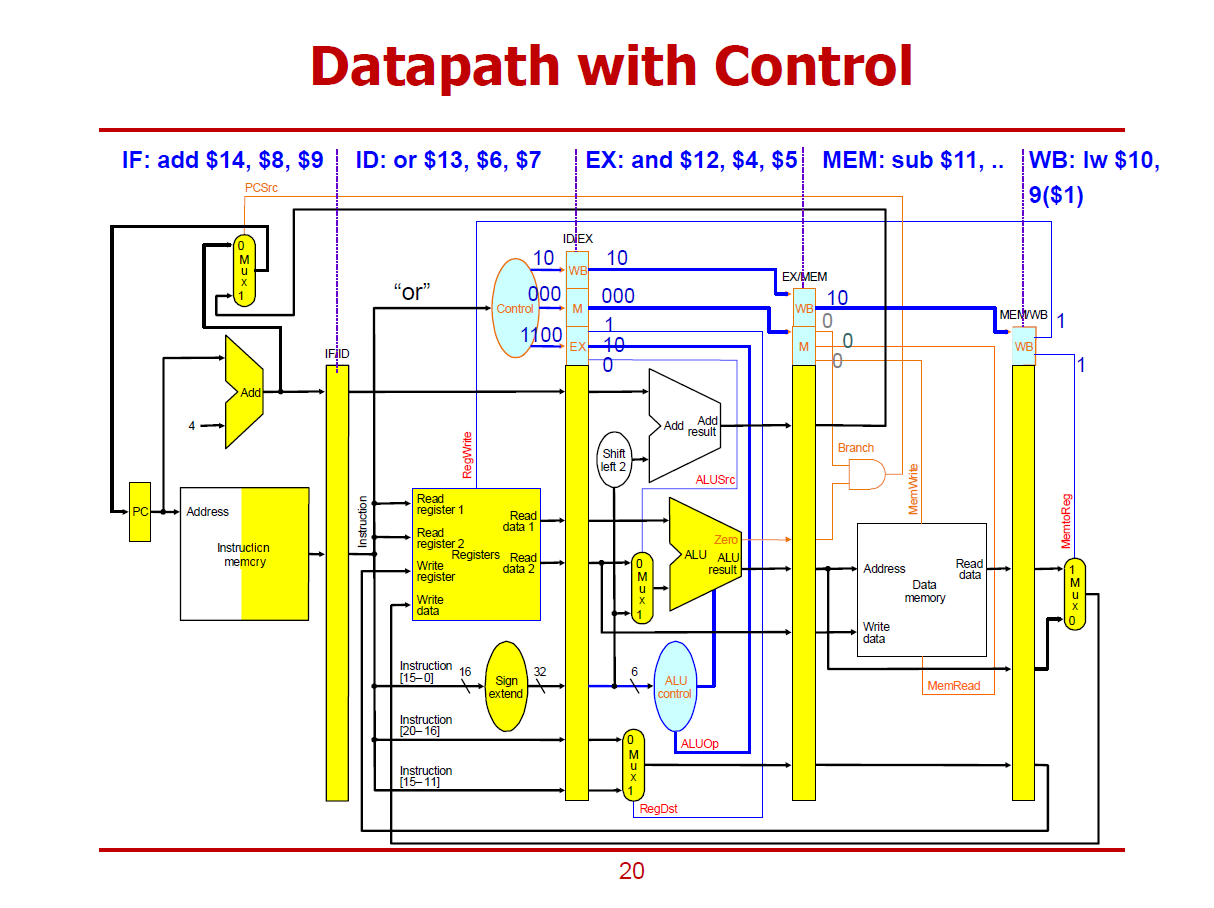

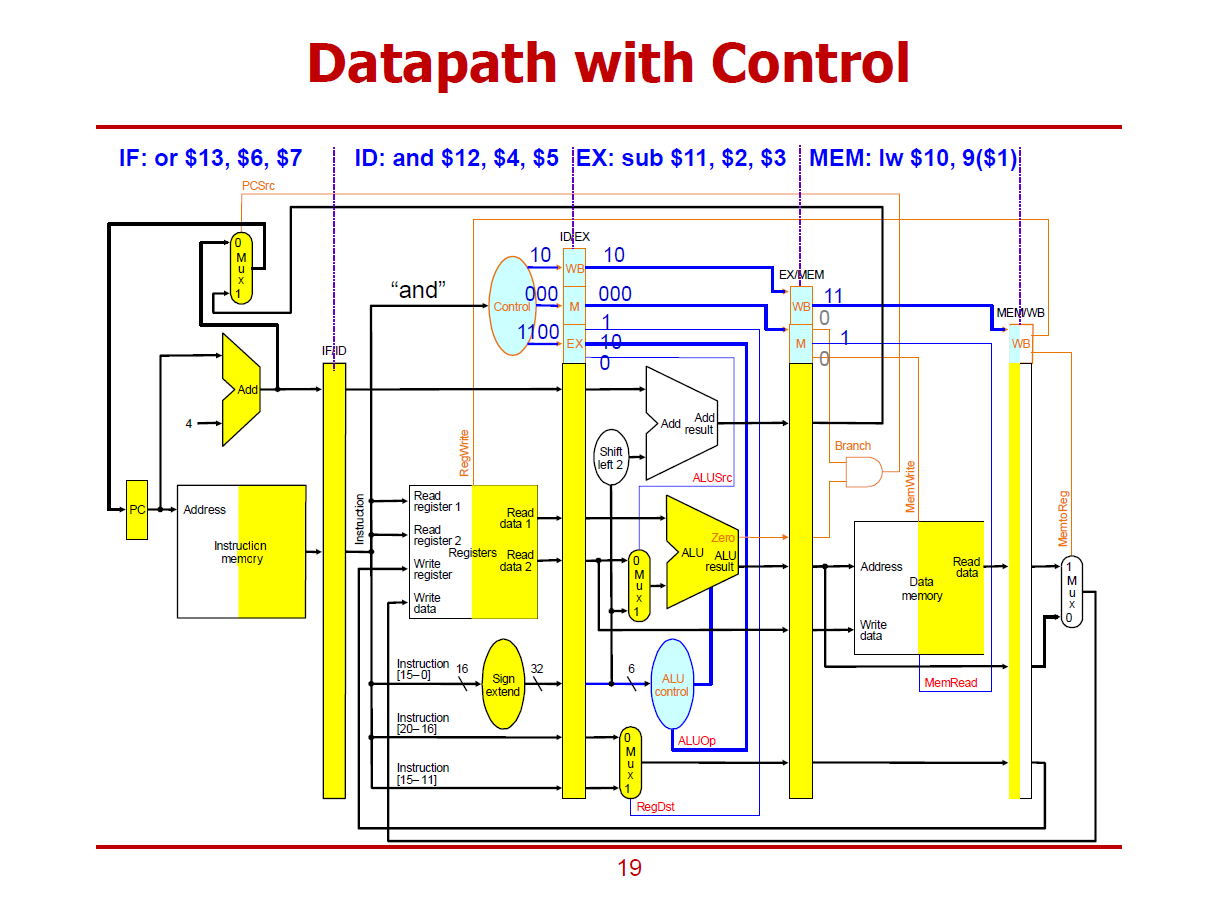

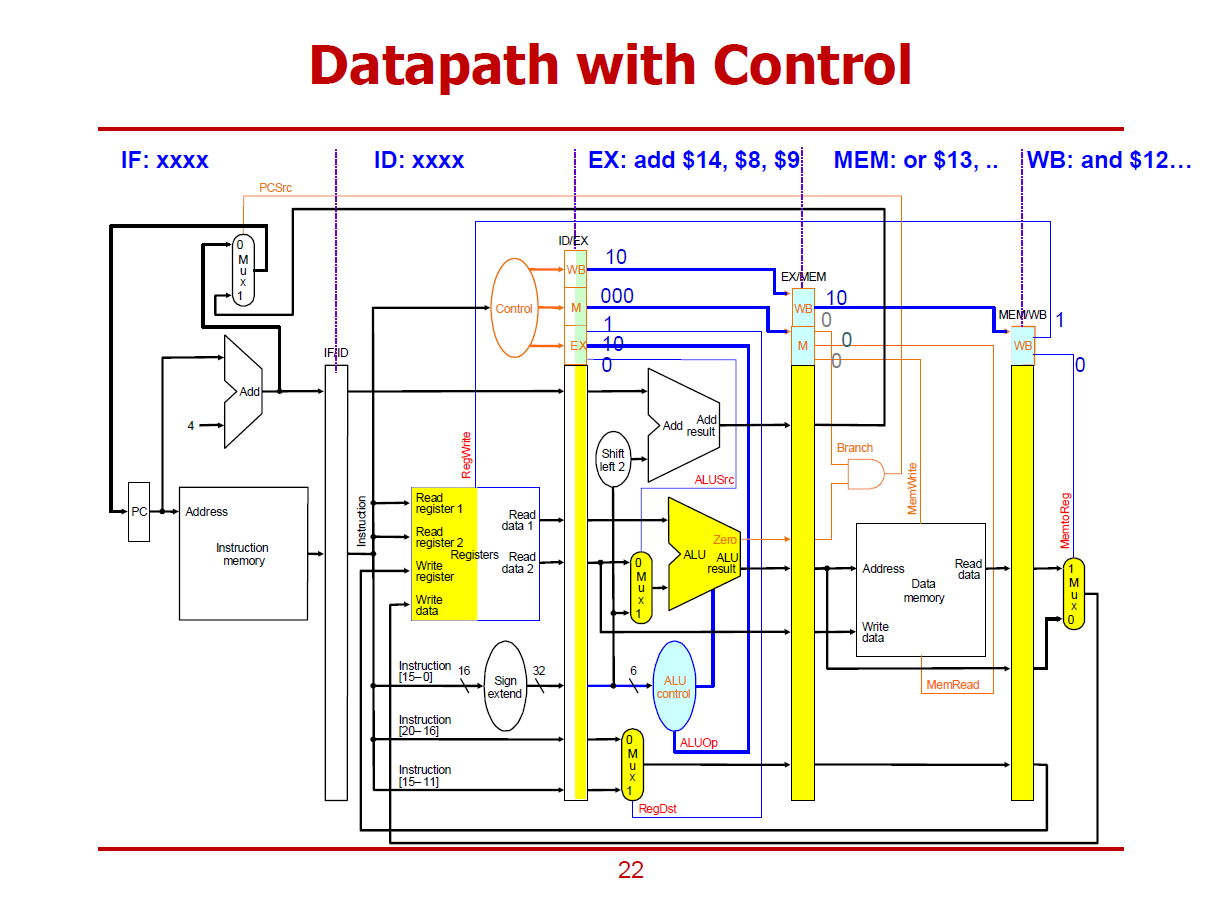

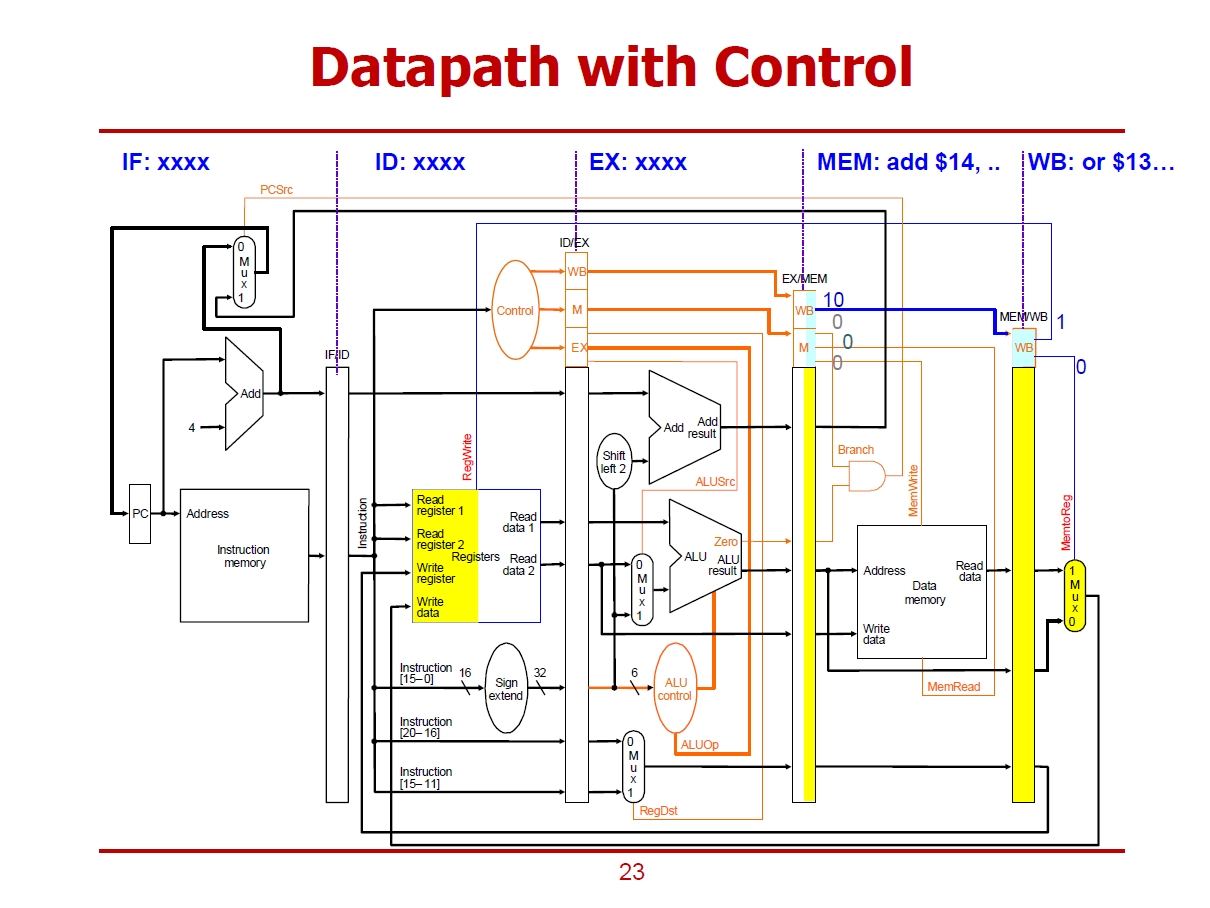

- ID Stage : \(\texttt{and}\) 명령어에 대한 Control 신호들을 생성한다.

- EX Stage : \(\texttt{sub}\) 명령어에 대한 Control 신호들이 사용되거나 MEM Stage로 넘겨진다.

- MEM Stage: \(\texttt{lw}\) 명령어에 대한 Control 신호들이 사용된다.

※ 본 포스트에서는 해저드를 고려하지 않았으므로, 각 명령어에 대한 Stage 진행이 단순히 이루어진 것이다.

Pipeline MIPS #1

- 회로내에 위치한 살구색 바는 Clock 신호에 동기화 된 다수의 Flip-Flops들로 구성된 Pipeline Register를 간단히 표현한 것이다.

- Pipeline Register은 범용 레지스터의 한 종류라 볼 수 있다.

- WB Stage 이후에는 파이프라인 레지스터가 없는 것을 확인할 수 있는데 이는, WB Stage에서는 레지스터에 값을 바로 쓰고 끝내기 때문에 별도의 파이프라인 레지스터가 필요하지 않다.

- 5개의 명령어가 제각기 다른 Stage를 처리하고 있는 모습을 표현한 그림이다. (해저드는 고려하지 않은 형태이다.)

- 위 그림에 해당되는 MIPS Assembly Code는 아래의 형태에 가까울 것이다.

\(\texttt{lw \$10, 20(\$1) ! IF Stage, 가장 먼저 실행된 명령어}\)

\(\texttt{sub \$11, \$2, \$3 ! ID Stage}\)

\(\texttt{add \$12, \$3, \$3 ! EX Stage}\)

\(\texttt{lw \$13, 24(\$1) ! MEM Stage}\)

\(\texttt{add \$14, \$5, \$6 ! 가장 늦게 실행된 명령어}\)

- \(\texttt{lw \$s0, 8(\$t1)}\) 명령어가 파이프라인 기반 MIPS H/W에서 동작되는 원리를 살펴본다.

- IF/ID 파이프라인 레지스터는 Instruction Memory에서 PC값에 해당되는 위치에 저장된 32bit 명령어를 가져오게 된다.

- IF/ID 파이프라인 레지스터는 또한, PC + 4에 해당되는 값을 입력받는다. (이는 명령어가 분기 명령어로 해석될 경우에 대비하여, 분기 주소 계산에 이용하기 위해 입력받는 것이다.)

- IF Stage에서는 Fetch한 명령어가 어떤 명령어인지 모르는 상태로 IF/ID 파이프라인 레지스터에 저장해놓게 된다.

- PC 또한 범용 레지스터이기 때문에, Clock 신호에 맞춰서 값을 입력받게 된다.

- Clock 신호가 들어오면, IF/ID 파이프라인 레지스터로부터 32bit의 명령어와 PC+4를 넘겨받게 된다.

- 32bit 명령어를 \(\texttt{lw}\) 명령어로 해석되는 절차는 그림에서 생략되었다.

- 레지스터 파일은 오로지 읽기 위해서만 접근하게 된다.

- Clock 신호가 들어오면, ID/EX 파이프라인 레지스터로부터 PC+4, 레지스터 출력, Sign-extend로 부터의 출력값을 넘겨 받게된다.

- 접근하고자 하는 Data Memory의 주솟값을 계산하는 Stage이다.

- 레지스터로부터 전달된 Base 주솟값과 Sign-Extension된 Offset값을 ALU가 더한다.(이 결과는 ALU result로써 출력된다.)

- ALU 위의 Adder는 분기 명령어를 처리할 때 분기 주소를 계산하기 위해 사용되는 Resource이기 때문에, \(\texttt{lw}\) 명령어를 처리할 때는 쓰이지 않는다.

- Clock 신호가 들어오면, EX/MEM 파이프라인 레지스터로부터 ALU result(메모리 주솟값)를 넘겨 받게된다.

- ALU result를 이용해 Data Memory 읽기 동작을 수행한다.

- Data Memory의 ALU result에 해당되는 위치에 저장된 값을 MEM/WB 파이프라인 레지스터에 넘긴다.

- Clock 신호가 들어오면, MEM/WB 파이프라인 레지스터로부터 Data Memory의 특정 위치에 저장된 값을 넘겨받게 된다.

- 넘겨받은 Read Data는 MUX를 거쳐서 레지스터의 특정 위치*(\(\texttt{\$s0}\) 레지스터)에 저장된다.

* 여기서 특정위치는 레지스터의 Write register에 해당되는데, 이 레지스터의 특정 위치가 WB Stage에서 입력되어야 하는데, ID Stage에서 Register 파일 읽기 동작을 수행할 때 입력되어 버려졌다.

즉, 위 그림에는 오류가 있다. (Write register 값이 WB Stage가 아닌, ID Stage에 입력되어 버렸다는 점)

※ 위 그림은 Data Memory로 부터 Load한 값을 다른 명령어의 Destination Field가 가리키는 레지스터에 저장하게 될 수도 있다. (사실, 어떤 오류가 생길 지 모른다.)

- 위 그림의 오렌지 색 Path처럼 Write register에 해당되는 값(Destination Field)이 WB Stage까지 유보되어야 정상적으로 메모리에서 Load한 값을 레지스터 파일에 저장할 수 있다.

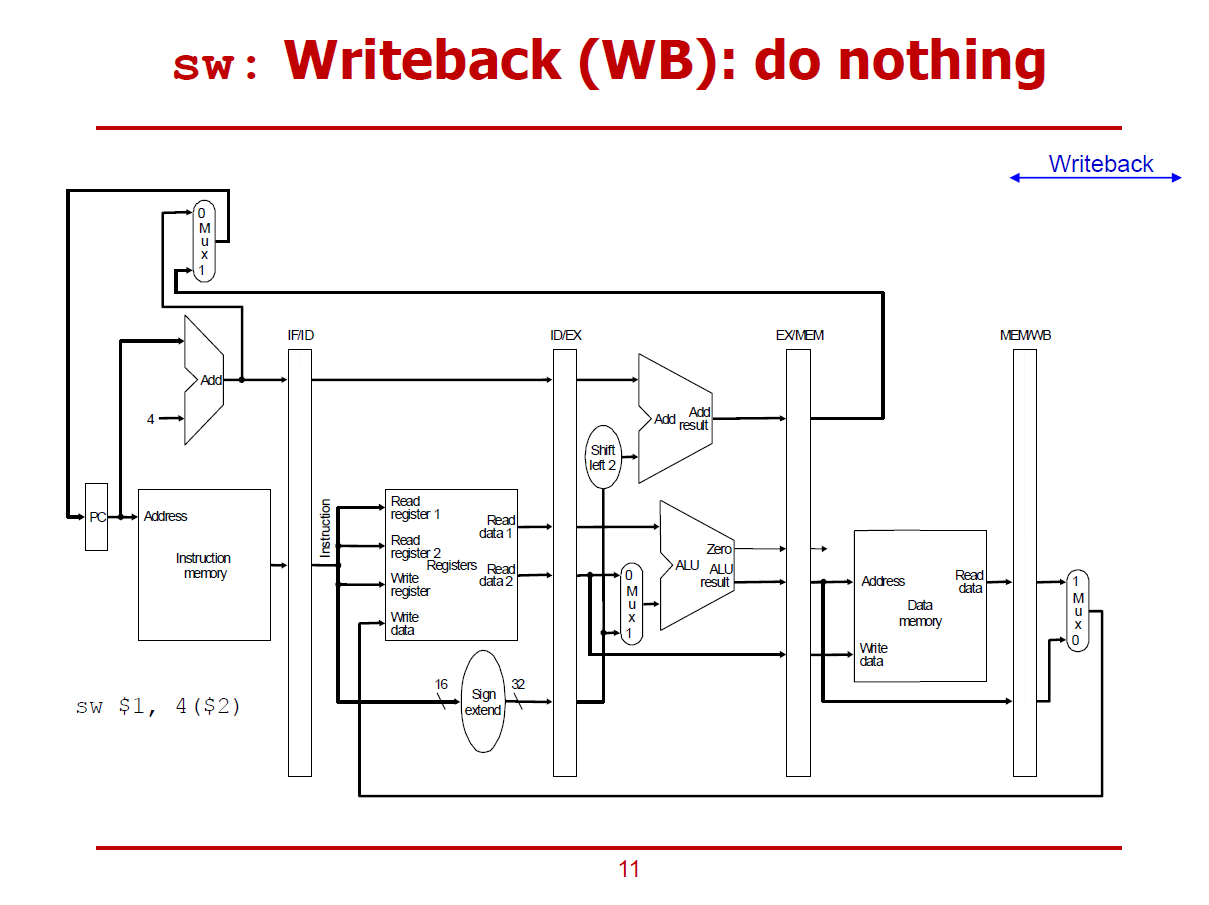

- \(\texttt{lw}\)와 달리, \(\texttt{sw}\) 명령어가 처리될 때의 차이점을 다룬다.

- MEM Stage에서의 \(\texttt{sw}\) 명령어는 \(\texttt{lw}\) 명령어와 달리, Data Memory 쓰기 동작을 수행한다.

- ID Stage에서 레지스터 파일 접근을 통해 읽은 데이터를 각각의 Stage들로부터 넘겨받아 Write Data 포트에 입력하게 된다.

- \(\texttt{sw}\) 명령어의 주소 계산(Base + Offset)은 \(\texttt{lw}\) 와 비슷하게 수행된다.

- \(\texttt{sw}\) 명령어는 WB Stage에서는 아무런 연산도 수행하지 않는다.

- 값을 메모리에 저장하는 연산이지, 레지스터에 저장하는 연산이 아니기 때문이다.

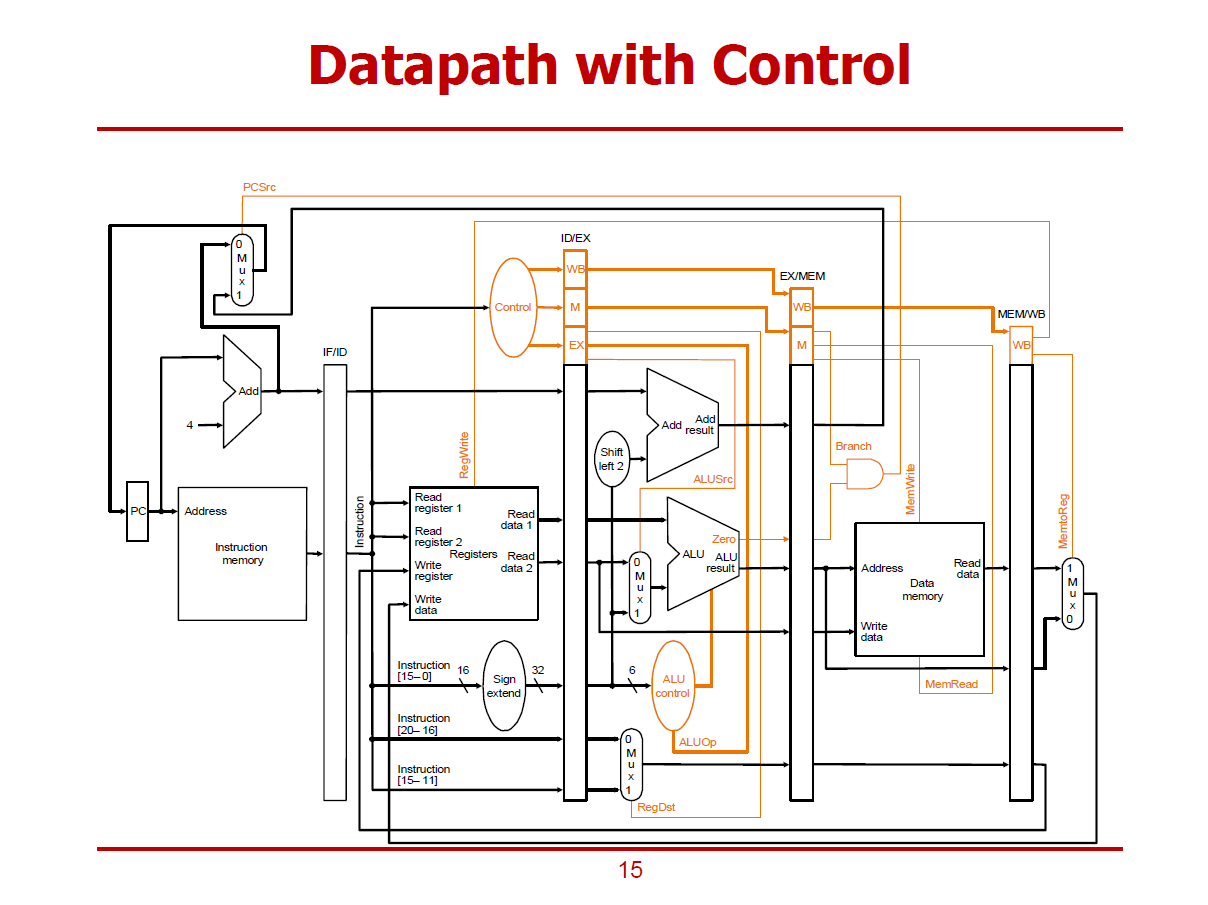

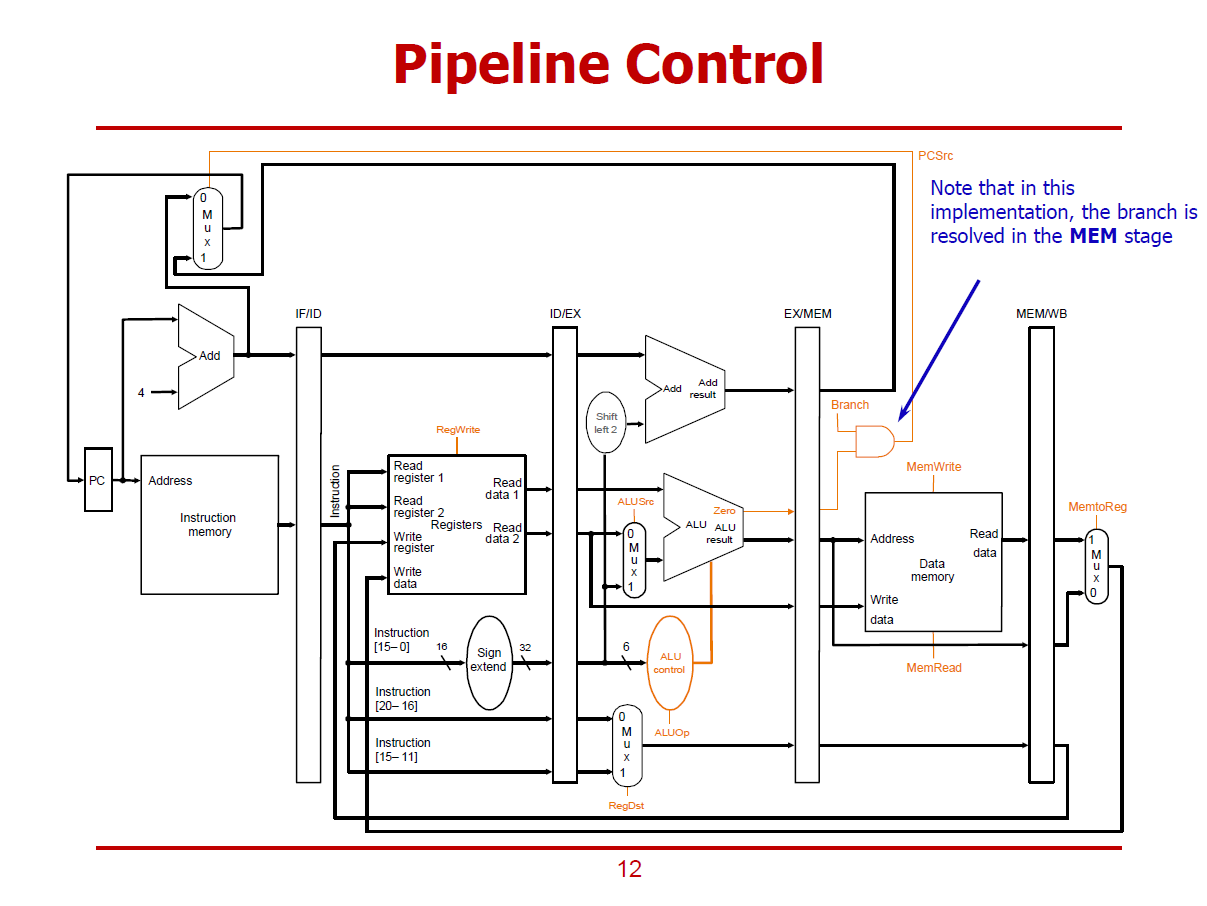

- Control Logic까지 반영하여 생각해본다.

- Control Logic은 대부분 MUX를 제어하거나, 메모리 쓰기 동작을 Enable하도록 하는 의도로 설계되었다.

- 각 Control 신호들은 자신들이 위치한 Stage에서 활용되어진다.

※ 단, RegWrite 신호는 실제로 ID Stage가 아닌, WB Stage에서 활용된다.

※ Branch 신호와 Zero 신호를 AND 연산한 PCSrc 또한, MEM Stage에서 활용하는 것으로 약속한다. (구현 방법에 따라 달라질 수 있다.)

- IF Stage에서는 어떠한 Control 신호도 필요없음을 확인할 수 있다.

- ID Stage에서도 어떠한 Control 신호도 필요없음을 확인할 수 있다. (RegWrite은 WB Stage에서 활용된다.)

- Control 신호들은 앞서 다뤘던 Single Cycle MIPS와 기능적인 측면에서는 동일하다.

- 각각의 Control 신호들이 어느 Stage에서 사용되는지를 나타낸 것이며, 생성 시기와는 무관하다.

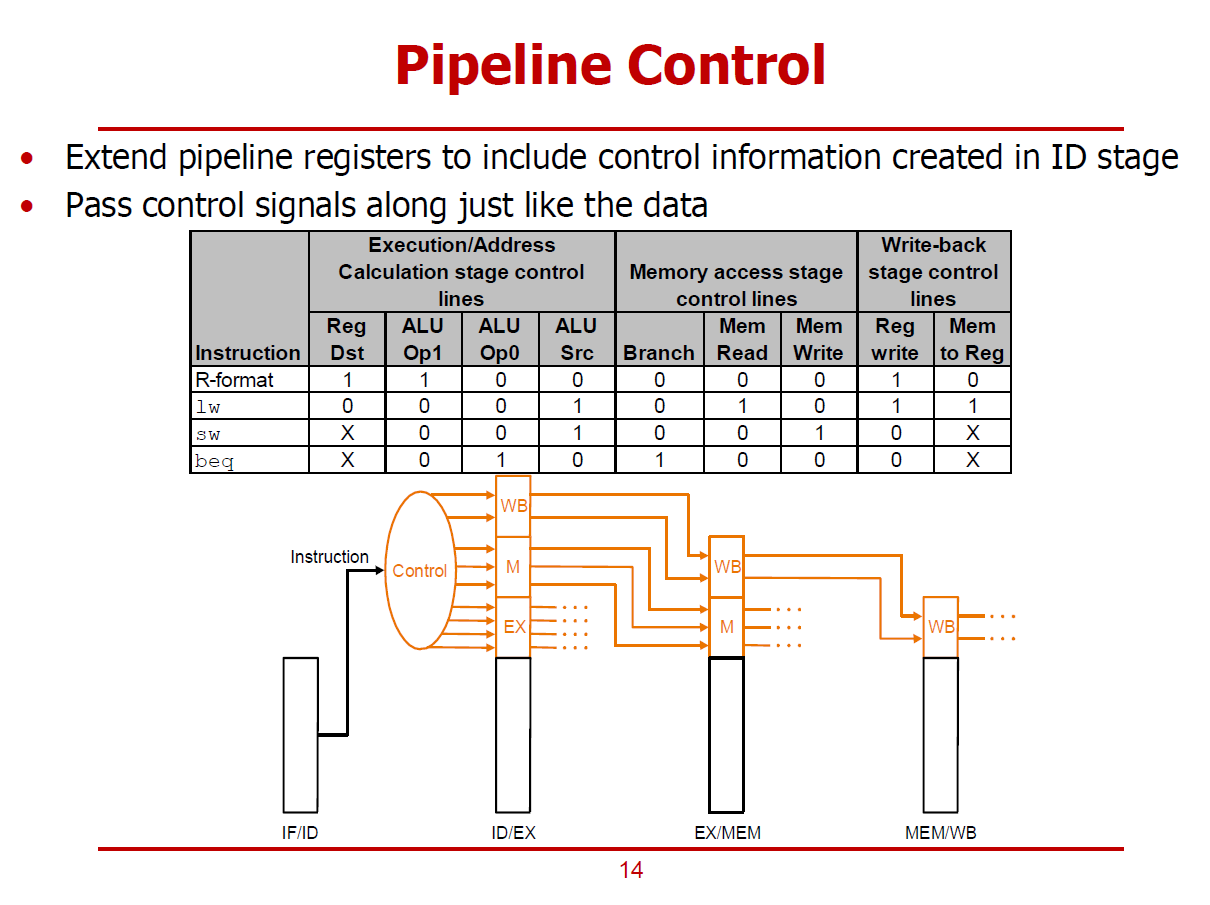

1. IF Stage

- 명령어를 무조건 Fetch하고, PC도 항상 4만큼 증가시키기 때문에 별도의 Control 신호를 필요로하지 않는다.

2. ID Stage

- 넘겨받은 명령어를 해석하고, 레지스터 파일에 접근, Immediate 값을 Extension 하는 작업만 수행하기 때문에 별도의 Control 신호를 필요로하지 않는다.

- 단, Control 신호를 생성할 수 있는 Stage이다. (명령어가 해석되는 단계이기 때문이다.)

3. EX Stage

- RegDst

- ALUop[1:0]

- ALUSrc

4. MEM Stage

- Branch

- MemRead

- MemWrite

5. WB Stage

- MemtoReg

- RegWrite

- Stage별로 다르게 사용되는 Control 신호들을 어떻게 생성하고 유지할 것인지에 대한 내용이다.

- 9개의 Control 신호가(ALUop[1:0]은 2개의 신호로 간주) 하나의 표로 정리되어 있다.

- 9개의 Control 신호들은 명령어의 OP-Code와 Funct Code를 통해 ID Stage에서 계산된다.

- 만들어진 Control 신호들은 ID Stage에서 사용되지 않고, 파이프라인 레지스터로 이동되어 알맞은 Stage에서 활용된다.

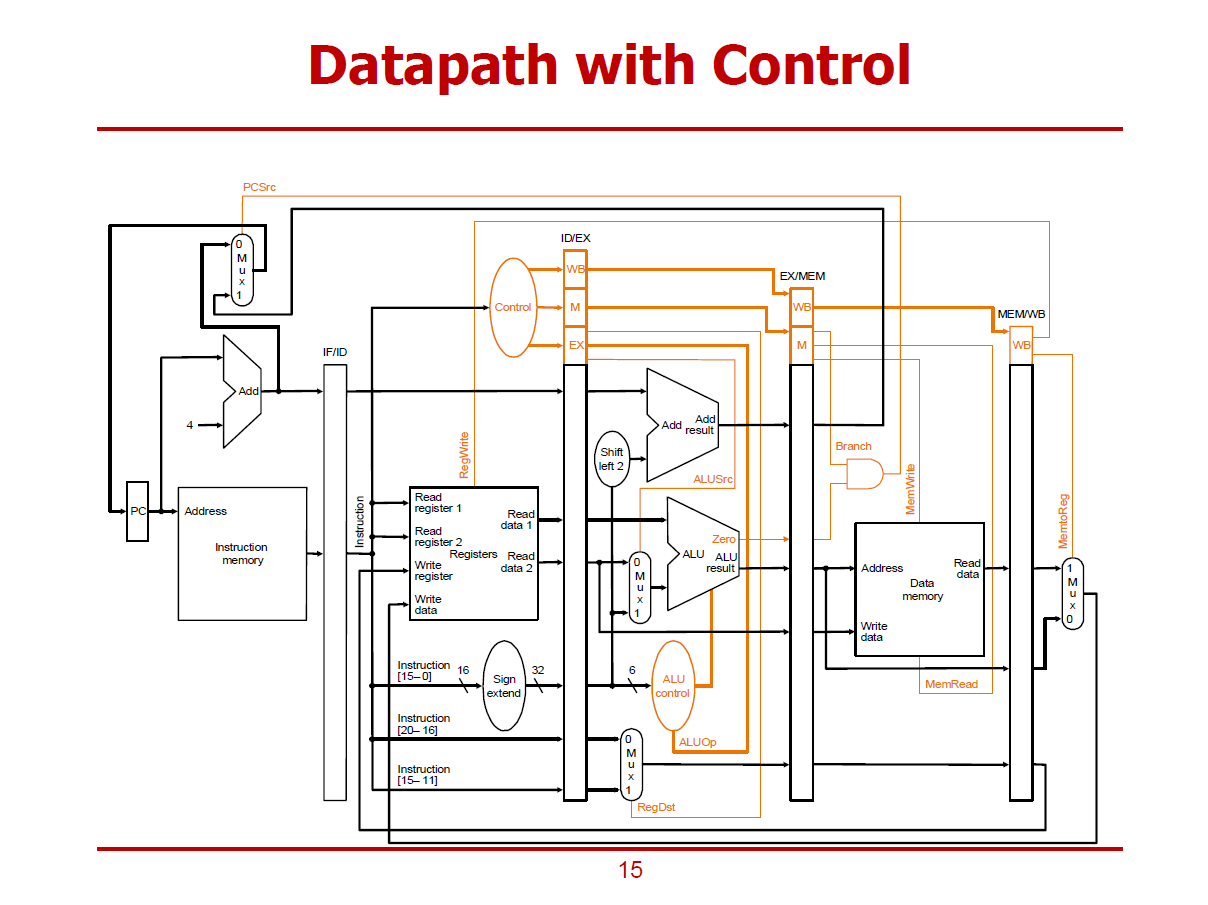

- Datapath와 Control 신호들이 모두 반영된 아키텍처 그림이다.

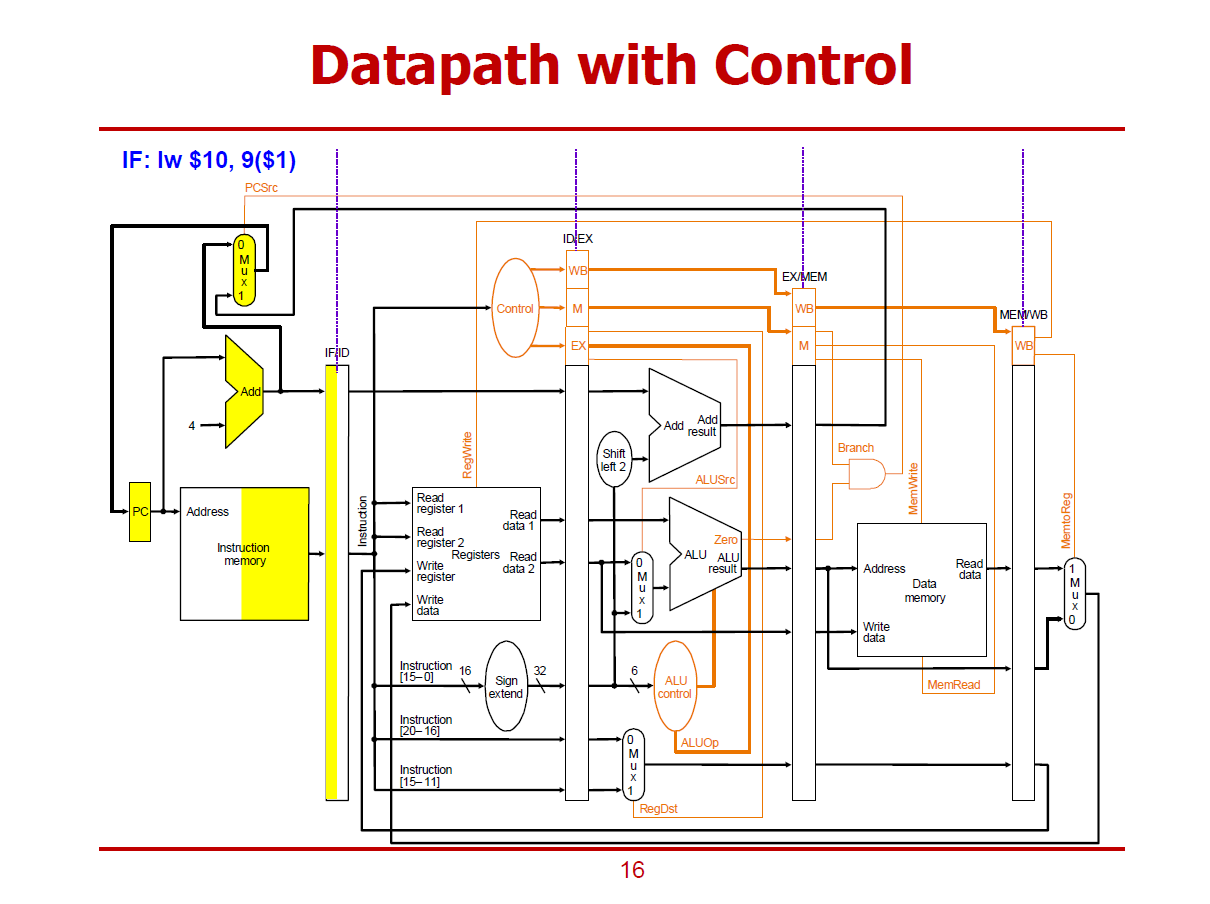

- \(\texttt{lw}\) 명령어가 처리되는 과정에서의 Data Path와 Control 신호들을 살펴본다.

- IF Stage에서는 Control 신호를 필요로 하지 않는다.

- 오로지, Instruction Memory로부터의 Fetch와, PC값을 4만큼 증가시키기만 한다.

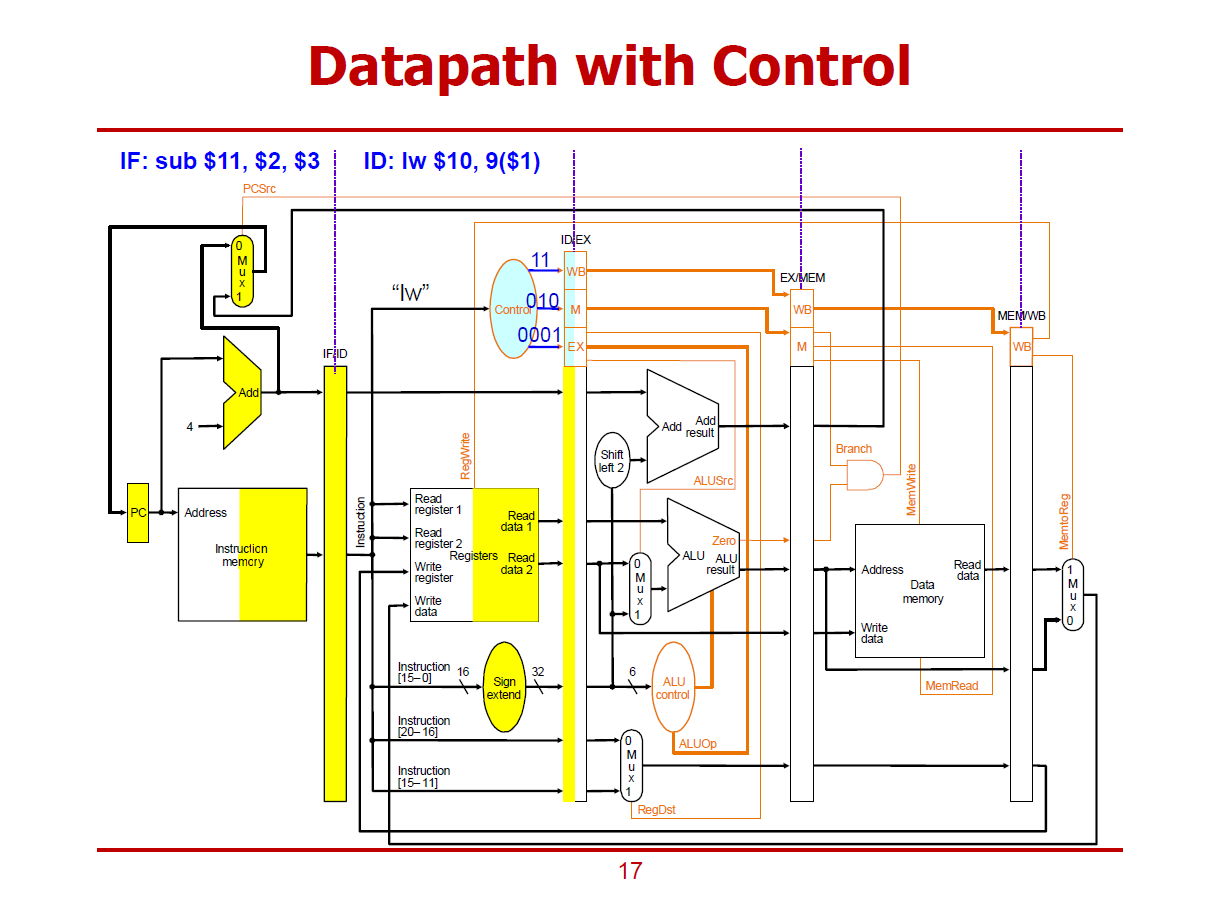

- 그 다음 클럭 사이클에서 \(\texttt{lw}\) 명령어는 ID Stage로 접어들고, \(\texttt{sub}\) 명령어가 IF Stage에 들어선다.

- ID Stage에서 해석된 \(\texttt{lw}\) 명령어는 9개의 Control 신호를 만들어낸다.

- ID Stage에서 생성된 Control 신호들은 자신이 사용될 Stage로 전달되기 위해 적절한 파이프라인 레지스터로 전달된다.

- 현재 그림에서 ID Stage에서는 \(\texttt{sub}\) 명령어에 대한 Control 신호들이 생성되고 있다.

- EX Stage에서는 이전에 생성되었던, \(\texttt{lw}\) 명령어에 대한 Control 신호들이 사용되거나 다음 Stage로 넘겨지고 있다.

- ID Stage : \(\texttt{and}\) 명령어에 대한 Control 신호들을 생성한다.

- EX Stage : \(\texttt{sub}\) 명령어에 대한 Control 신호들이 사용되거나 MEM Stage로 넘겨진다.

- MEM Stage: \(\texttt{lw}\) 명령어에 대한 Control 신호들이 사용된다.

※ 본 포스트에서는 해저드를 고려하지 않았으므로, 각 명령어에 대한 Stage 진행이 단순히 이루어진 것이다.