Decoder

디코더

- 여러 개의 입력을 받아 어느 특정 입력에 대한 어느 특정 출력만을 활성화시키는 회로이다.

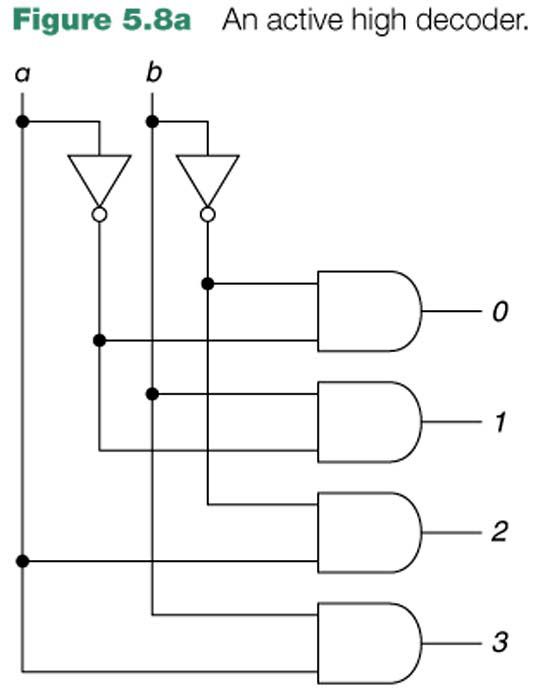

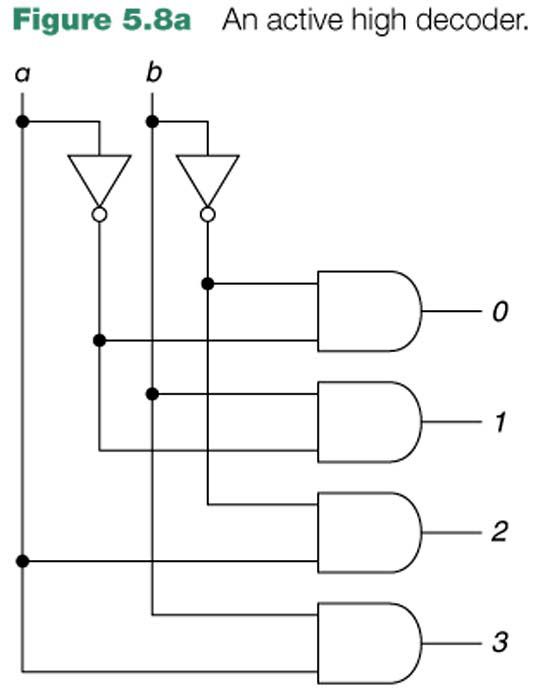

Active High Decoder

- 이진수 값을 십진수 값으로 나타낼 때, True(1)값을 이용하여 나타내는 회로이다.

1. 2 to 4 Decoder

a. Truth Table

| Inputs (BCD Code) |

Outputs (Decimal Digit) |

||||

| \(a\) | \(b\) | \(0_{(10)}\) | \(1_{(10)}\) | \(2_{(10)}\) | \(3_{(10)}\) |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

b. Circuit Implementation

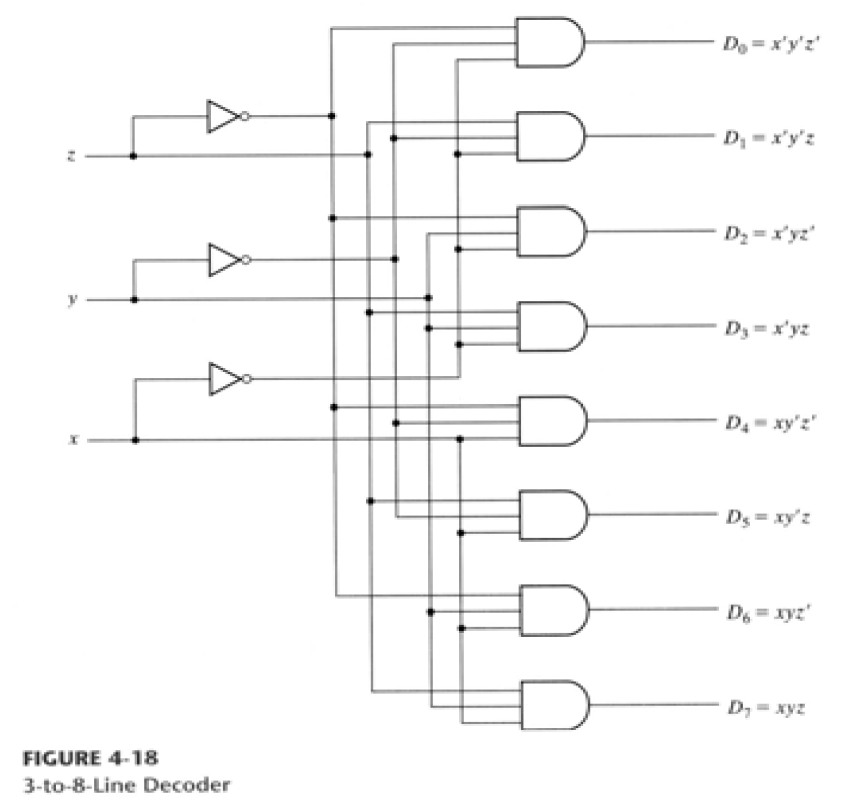

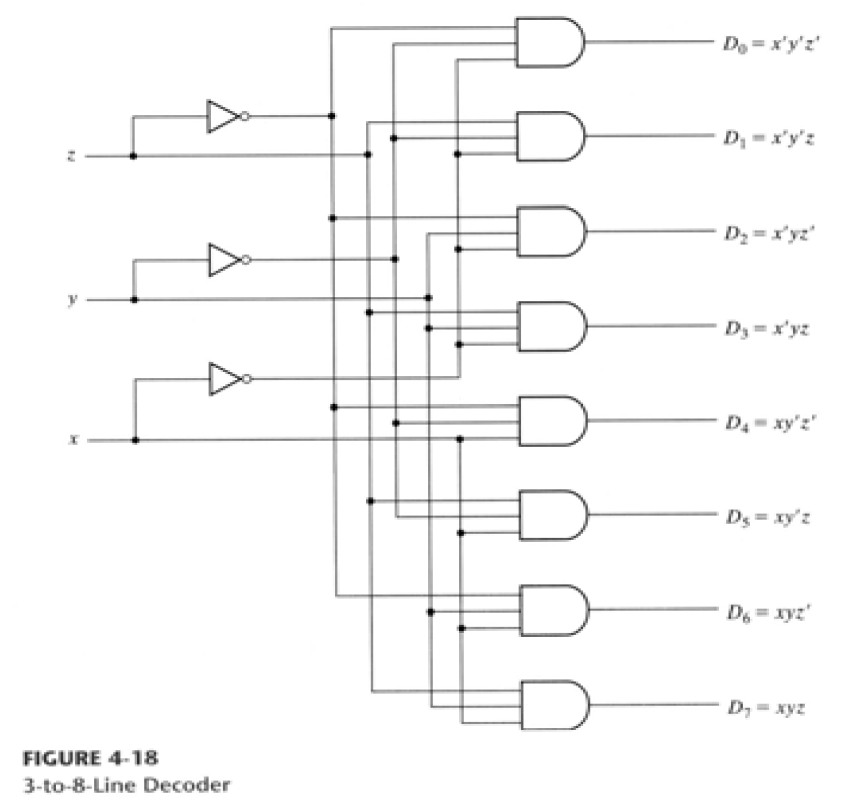

2. 3 to 8 Decoder

a. Truth Table

| Inputs (BCD Code) |

Outputs (Decimal Digit) |

|||||||||

| \(x\) | \(y\) | \(z\) | \(D_0\) | \(D_1\) | \(D_2\) | \(D_3\) | \(D_4\) | \(D_5\) | \(D_6\) | \(D_7\) |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

b. Circuit Implementation

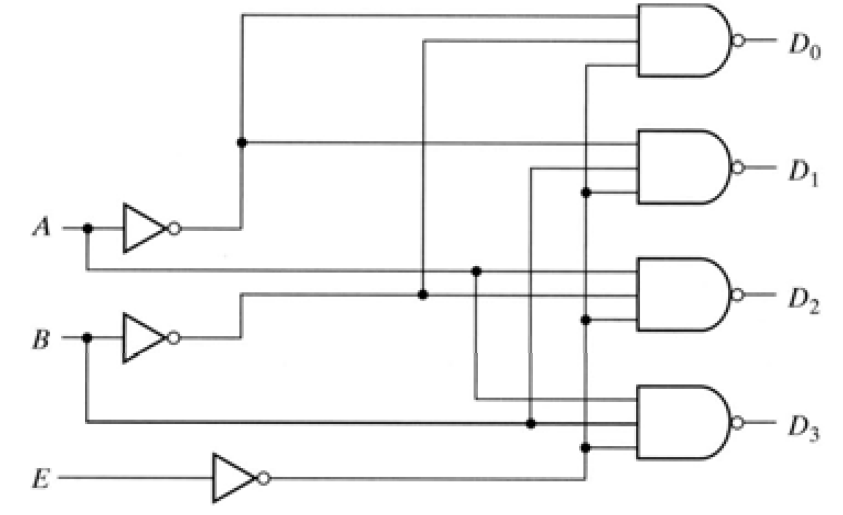

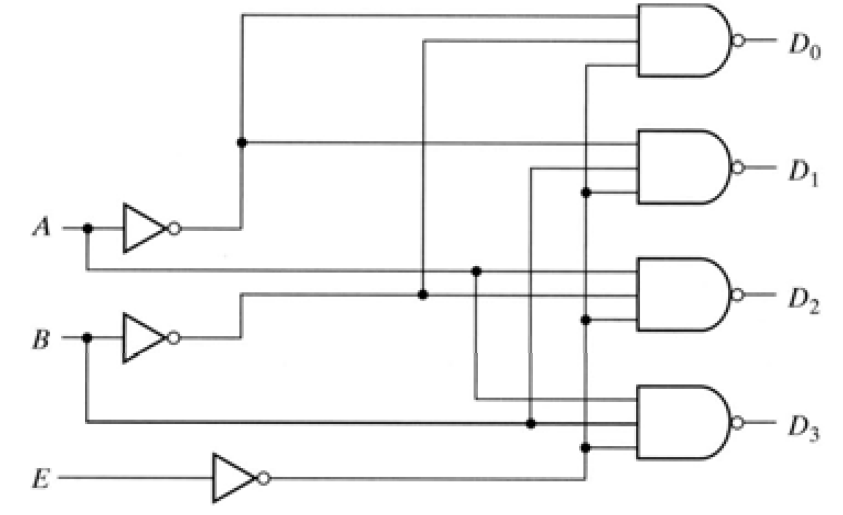

Active Low Decoder

- 이진수 값을 십진수 값으로 나타낼 때, False(0)값을 이용하여 나타내는 회로이다.

1. 2 to 4 Decoder

a. Truth Table

| Inputs (BCD Code) |

Outputs (Decimal Digit) |

|||||

| \(E\) (Enable Signal) |

\(A\) | \(B\) | \(D_0\) | \(D_1\) | \(D_2\) | \(D_3\) |

| 1 | X | X | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 |

b. Circuit Implementation

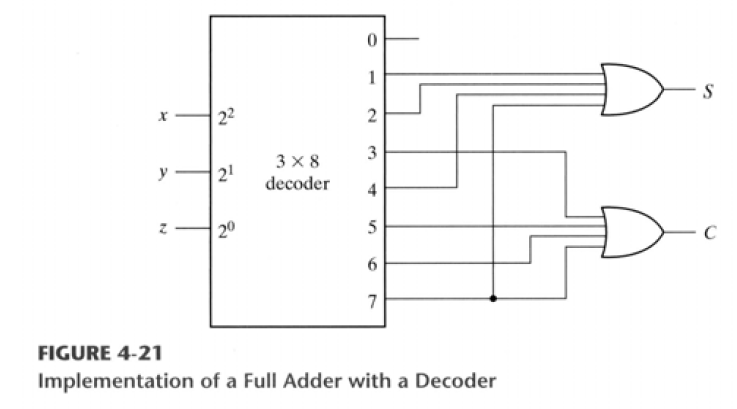

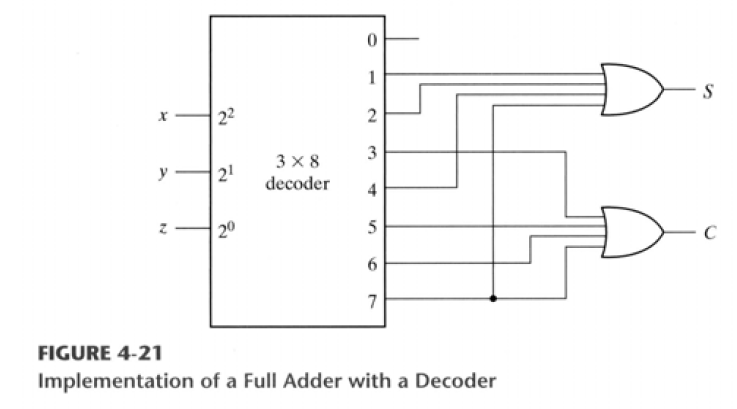

Full Addre with 3 to 8 Decoder

\(S(x, y, z) = \sum\limits (1, 2, 4, 7)\)

\(C(x, y, z) = \sum\limits (3, 5, 6, 7)\)

Reference: Fundamentals of DIGITAL LOGIC with VHDL Design 3E (Stephen Brown, Zvonko Vranesic 저, Mc Graw Hill, 2009)

Decoder

디코더

- 여러 개의 입력을 받아 어느 특정 입력에 대한 어느 특정 출력만을 활성화시키는 회로이다.

Active High Decoder

- 이진수 값을 십진수 값으로 나타낼 때, True(1)값을 이용하여 나타내는 회로이다.

1. 2 to 4 Decoder

a. Truth Table

| Inputs (BCD Code) |

Outputs (Decimal Digit) |

||||

| \(a\) | \(b\) | \(0_{(10)}\) | \(1_{(10)}\) | \(2_{(10)}\) | \(3_{(10)}\) |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

b. Circuit Implementation

2. 3 to 8 Decoder

a. Truth Table

| Inputs (BCD Code) |

Outputs (Decimal Digit) |

|||||||||

| \(x\) | \(y\) | \(z\) | \(D_0\) | \(D_1\) | \(D_2\) | \(D_3\) | \(D_4\) | \(D_5\) | \(D_6\) | \(D_7\) |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

b. Circuit Implementation

Active Low Decoder

- 이진수 값을 십진수 값으로 나타낼 때, False(0)값을 이용하여 나타내는 회로이다.

1. 2 to 4 Decoder

a. Truth Table

| Inputs (BCD Code) |

Outputs (Decimal Digit) |

|||||

| \(E\) (Enable Signal) |

\(A\) | \(B\) | \(D_0\) | \(D_1\) | \(D_2\) | \(D_3\) |

| 1 | X | X | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 |

b. Circuit Implementation

Full Addre with 3 to 8 Decoder

\(S(x, y, z) = \sum\limits (1, 2, 4, 7)\)

\(C(x, y, z) = \sum\limits (3, 5, 6, 7)\)

Reference: Fundamentals of DIGITAL LOGIC with VHDL Design 3E (Stephen Brown, Zvonko Vranesic 저, Mc Graw Hill, 2009)