Decoder Modeling

디코더 모델링

Example. NOT Gate(Inverter) Implementation

USE work.std_logic_1164.all;

ENTITY inv IS

PORT( a : IN std_logic;

b : OUT std_logic );

END inv;

ARCHITECTURE behave OF inv IS

BEGIN

b <= NOT(a) AFTER 5 ns;

END behave;

CONFIGURATION invcon OF inv IS

FOR behave

END FOR;

END invcon;

Example. AND Gate Implementation

USE work.std_logic_1164.all;

ENTITY and3 IS

PORT( a1, a2, a3 : IN std_logic;

o1 : OUT std_logic );

END and3;

ARCHITECTURE behave OF and3 IS

BEGIN

o1 <= a1 AND a2 AND a3 AFTER 5ns;

END behave;

CONFIGURATION and3con OF and3 IS

FOR behave

END FOR;

END and3con;

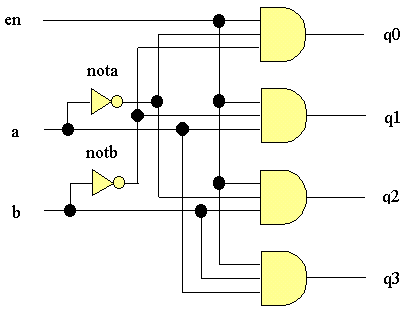

Example. 2 to 4 Decoder Implementation (Structural Modeling)

| Inputs | Outputs | ||||

| a | b | q0 | q1 | q2 | q3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

USE work.std_logic_1164.all;

ENTITY decode IS

PORT( a, b, en : IN std_logic; -- en: enable

q0, q1, q2, q3 : OUT std_logic );

END decode;

ARCHITECTURE structural OF decode IS

COMPONENT inv

PORT( a : IN std_logic;

b : OUT std_logic );

END COMPONENT;

COMPONENT and3

PORT( a1, a2, a3 : IN std_logic;

o1 : OUT std_logic );

END COMPONENT;

SIGNAL nota, notb : std_logic;

BEGIN

i1 : inv PORT MAP (a, nota);

i2 : inv PORT MAP (b, notb);

a1 : and3 PORT MAP (nota, en, notb, q0);

a2 : and3 PORT MAP (a, en, notb, q1);

a3 : and3 PORT MAP (nota, en, b, q2);

a4 : and3 PORT MAP (a, en, b, q3);

END structural;

* Low-Level Configuration

-- Specifies lower-level configurations for each component

CONFIGURATION decode_llcon OF decode IS

FOR structural

FOR i1 : inv

USE CONFIGURATION work.invcon;

END FOR;

FOR i2 : inv

USE CONFIGURATION work.invcon;

END FOR;

FOR all : and3

USE CONFIGURATION work.and3con;

END FOR;

END FOR;

END decode_llcon;

* Entity-Architecture Pair Configuration (

CONFIGURATION decide_eacon OF decode IS

FOR structural

FOR i1 : inv

USE ENTITY work.inv(behave);

END FOR;

FOR OTHERS : inv

USE ENTITY work.inv(behave);

END FOR;

FOR a1 : and3

USE ENTITY work.and3(behave);

END FOR;

FOR OTHERS : and3

USE ENTITY work.and3(behave);

END FOR;

END FOR;

END decode_eacon;

※ Port의 이름이 다를 경우, Configuration 구문에서 Named Association Port Mapping을 통해 쉽게 대응할 수 있다.

USE work.std_logic_1164.all;

ENTITY inv IS

PORT( x : IN std_logic;

y : OUT std_logic );

END inv;

ARCHITECTURE behave OF inv IS

BEGIN

y <= NOT(x) AFTER 5ns;

END behave;

CONFIGURATION invcon OF inv IS

FOR behave

END FOR;

END invcon;

-- Mapping Ports

CONFIGURATION decode_map_con OF decode IS

FOR structural

FOR i1 : inv

USE ENTITY work.inv(behave) PORT MAP (a => x, b => y);

END FOR;

FOR i2 : inv

USE ENTITY work.inv(behave) PORT MAP (a => x, b => y);

END FOR;

FOR ALL : and3

USE ENTITY work.and3(behave);

END FOR;

END FOR;

END decode_map_con;Another Implementation

| Inputs | Outputs | ||||

| A | B | o0 | o1 | o2 | o3 |

| 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

1) if Statement

ENTITY decoder2x4 IS

PORT( i : IN bit_vector(1 DOWNTO 0);

o : OUT bit_vector(3 DOWNTO 0) );

END decoder2x4;

ARCHITECTURE design_if OF decoder2x4 IS

BEGIN

PROCESS(i)

BEGIN

IF (i = "00") THEN

o <= "0001"; -- o(0) -> 1

ELSIF (i = "01") THEN -- i(1) -> 0, i(0) -> 1

o <= "0010"; -- o(1) -> 1

ELSIF (i = "10") THEN -- i(1) -> 1, i(0) -> 0

o <= "0100"; -- o(2) -> 1

ELSE

o <= "1000"; -- o(3) -> 1

END IF;

END PROCESS;

END design_if;

2) case Statement

ENTITY decoder2x4 IS

PORT( i : IN bit_vector(1 DOWNTO 0);

o : OUT bit_vector(3 DOWNTO 0) );

END decoder2x4;

ARCHITECTURE design_case OF decoder2x4 IS

BEGIN

PROCESS(i)

BEGIN

CASE(i) IS

WHEN "00" => o <= "0001";

WHEN "01" => o <= "0010";

WHEN "10" => o <= "0100";

WHEN OTHERS => o <= "1000";

END CASE;

END PROCESS;

END design_case;

3) with-select0when Statement

ENTITY decoder2x4 IS

PORT( i : IN bit_vector(1 DOWNTO 0);

o : OUT bit_vector(3 DOWNTO 0) );

END decoder2x4;

ARCHITECTURE design_with OF decoder2x4 IS

BEGIN

WITH i SELECT

o <= "0001" WHEN "00",

"0010" WHEN "01",

"0100" WHEN "10",

"1000" WHEN OTHERS;

END design_with;

4) when-else Statement