Moore Model and Mealy Model

무어 모델과 밀리 모델

* Analysis of Clocked Sequential Circuit

1) 회로에서 Flip-Flop의 Input/Output에 대한 State Equation을 구한다.

2) State Equation들로부터 State Table을 구성한다.

3) Timing Diagram과 State Diagram을 구성한다.

- Moore Model: Output이 Present State에 의해서만 변한다.

- Mealy Model: Output이 Present State와 Input에 의해 변한다.

Moore FSM

- Output이 오직 FFs의 Present State에 의해서만 결정된다.

- Output은 Clock에 Synchronized되어 있다.

Example. D FFs Moore Circuit

1) State Equation

\(D_1 = q_1q_2' + xq_1'\)

\(D_2 = xq_1\)

\(z = q_2'\)

2) State Table

3) State Diagram

Mealy FSM

- Output이 Input과 FFs의 Present State에 의해 결정된다.

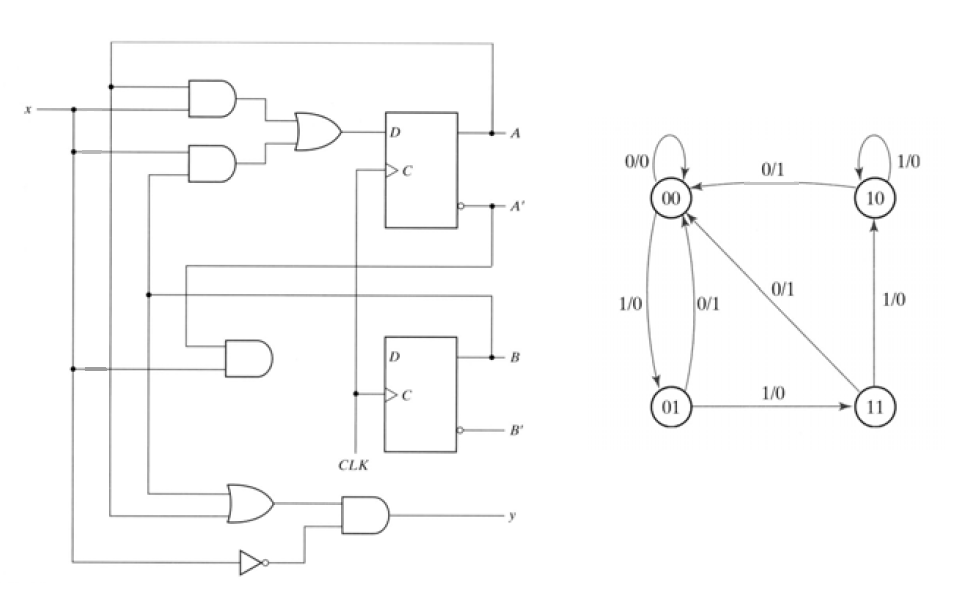

Example. D FFs Mealy Circuit

1) State Equation

\(D_1 = xq_1 + xq_2\)

\(D_2 = xq_1'q_2'\)

\(z = xq_1\)

\(q_1^* = xq_1 + xq_2\)

\(q_2^* = xq_1'q_2'\)

2) State Table

\(q : q_1q_2\)

\(q^* : q_1^*q_2^*\)

3) State Diagram

4) Trace Timing and Timing Diagram

- Input \(x\)가 Clock 신호와 동시에 바뀌지 않아, false output이 발생되었다.

- Mealy Model에서는 Clock Edge에서 "Output"이 중요하기 때문에 큰 문제가 되지는 않는다.