Sequential Circuit Design Procedure

순차 회로 설계 과정

Step 1. From the specification, find a state diagram.

- Specification으로부터 State Diagram을 구성한다.

Step 2. Reduce the # of states (Optional)

- State 개수를 최적화(최소화)한다.

- 선택적이며, 가장 힘든 단계이다.

Step 3. Binary state assignment

- State에 Binary 번호를 할당한다.

Step 4. Find state table

- State Table을 구성한다.

Step 5. Choose FFs

- 사용할 Flip-Flops을 선정한다.

Step 6. Input and output equations

- State Table을 통해 Input, Output Equation을 수립한다.

Step 7. Draw logic diagram

- Unit Cell, Simple Cell을 통해 Logic Diagram을 구성한다.

* Synthesis : Step 3 ~ Step 7

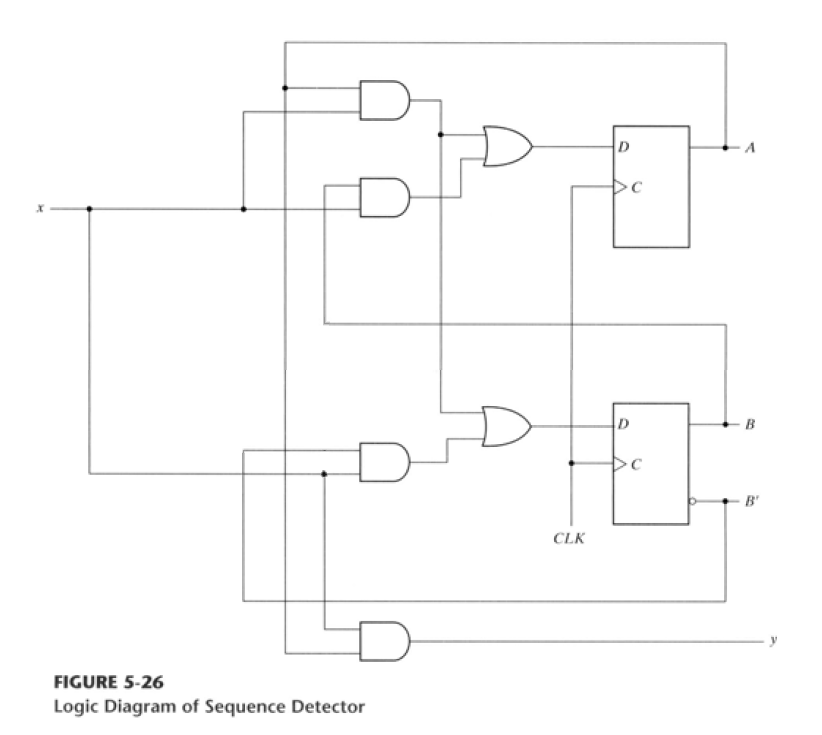

Example. Sequence Detector

Specification

A circuit that detects three or more consecutive 1's in a string of bit coming through an input line.

- 상태 S_3일 때, 1을 출력하고, 나머지 상태에서는 0을 출력한다.

Step 1. State Diagram

Step 2. Reduce the # of states

- 더 이상 최적화할 수 없다.

Step 3. Binary state assignment (Renaming)

\(S_0 = 00\)

\(S_1 = 01\)

\(S_2 = 10\)

\(S_3 = 11\)

Step 4. Find state table

| Present State | Input | Next State | Output | ||

| A | B | x | A (\(D_A\)) | B (\(D_B\)) | y |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 |

Step 5. Choose FFs

- D Flip-Flop을 회로 구성에 이용한다.

- 이번 Cycle에서의 Next State가 그대로 다음 Cycle의 Present State가 된다. (D-FFs의 특성)

Step 6. Input and output equations

\(D_A = \sum (3, 5, 7) = Ax + Bx\)

\(D_B = \sum (1, 5, 7) = Ax + B'x\)

\(y = \sum (5, 7) = Ax\)

Step 7. Draw logic diagram

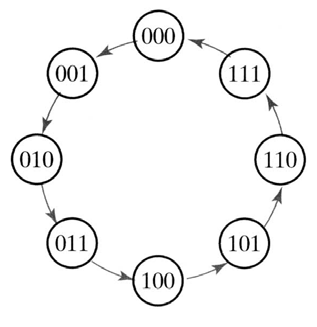

Example. 3-Bits Binary Counter

Specification

Step 1. From the specification, find a state diagram.

Step 2. Reduce the # of states

- 더 이상 최적화할 수 없다.

Step 3. Binary state assignment

- Specification에서 이미 State에 Binary Number가 부여되었다.

Step 4. Find state table

* Excitation Table of T-FFs

| Q(t) | Q(t+1) | T |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Step 5. Choose FFs

- T Flip-Flop을 회로 구성에 이용한다.

Step 6. Input and output equations

\(T_{A2} = A_1A_0\)

\(T_{A1} = A_0\)

\(T_{A0} = 1\)

Step 7. Draw logic diagram