Full Adder Modeling

전가산기 모델링

- 세 개의 입력 A, B, Z와 두 개의 출력 Carry(C), Sum(S)을 가진다.

- Z는 아래 자릿 수에서의 덧셈의 결과로 파생된 Carry를 의미한다.

Truth Table for FA

| Inputs | Outputs | |||

| Z | A | B | C | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

* Binary Adder - Full Adder (URL)

Full Adder - Behavioral Model

-- Entity Declaration

ENTITY Full_Adder IS

PORT (X, Y, Z : IN bit;

S, C : OUT bit );

END Full_Adder;

-- Architecture Body

ARCHITECTURE Behavioral_Design OF Full_Adder IS

BEGIN

PROCESS (X, Y, Z)

variable I : integer;

begin

I := 0;

if ( X = '1' ) then I := I+1; end if

if ( Y = '1' ) then I := I+1; end if

if ( Z = '1' ) then I := I+1; end if

if ( (I=0) or (I=2) ) then

S <= '0' after 2 ns;

else S <= '1' after 2 ns;

end if

if ( (I=0) or (I=1) ) then

C <= '0' after 2 ns;

else C <= '1' after 2 ns;

end if

END PROCESS

END Behavioral_Design; Full Adder - Dataflow Model

-- Entity Declaration

ENTITY Full_Adder IS

PORT( X, Y, Z : IN bit;

S, C : OUT bit );

END Full_Adder;

-- Architecture Body

ARCHITECTURE Dataflow_Design OF Full_Adder IS

BEGIN

S <= X xor Y xor Z after 2 ns:

C <= (X and Y) or (X and C) or (Y and C) after 2 ns;

END Dataflow_Design;

* AB'Z + A'BZ + AB = AB + BZ + AZ

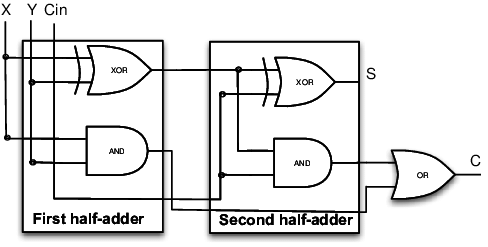

Full Adder - Structural Model

- FA의 모든 Component를 AND, OR 게이트만으로 구성할 수 있으며,

AND, OR, XOR 게이트를 이용하여 구성할 수도 있다.

- 본 포스트에서는 2개의 HA와 하나의 OR 게이트로 구성된 FA를 VHDL로 표현한다.

-- Entity Declaration

ENTITY Full_Adder IS

PORT( X, Y, Cin : IN bit;

S, C : OUT bit );

END Full_Adder;

-- Architecture Body

ARCHITECTURE Structural_Design OF Full-Adder IS

-- Declaration of local signals

signal t_s, t_c1, t_c2 : bit;

-- Component Declarations

component OR2

port( I1, I2 : IN bit;

O : OUT bit );

end component

component Half_Adder

port( A, B : IN bit;

Sum, Carry : OUT bit );

end component

// Component Instantiation

BEGIN

HA1 : Half_Adder port map( X, Y, t_s, t_c1 ); -- Positional Association (위치 결합)

HA2 : Half_Adder port map( t_s, Cin, S, t_c2 ); -- Positional Association (위치 결합)

ORG : OR2 port map( t_c1, t_c2 C ); -- Positional Association (위치 결합)

END Structural_Design;- Local Signal t_s, t_c1, t_c2는 모두 Component들을 연결하는 신호들이다.

- \(\texttt{t_s}\) : First Half-Adder에서 XOR 게이트의 출력값 (1st HA의 \(\texttt{Sum}\)값)

- \(\texttt{t_c1}\) : First Half-Adder에서 AND 게이트의 출력값 (1st HA의 \(\texttt{Carry}\)값)

- \(\texttt{t_c2}\) : Second Half-Adder에서 AND 게이트의 출력값 (2nd HA의 \(\texttt{Carry}\)값)

* Named Association Type Mapping

HA1 : Half_Adder port map (A=>X, B=>Y, Sum=>t_s, Carry=>t_c1);

HA1 : Half_Adder port map (A=>t_s, B=>Cin, Sum=>S, Carry=>t_c2);

ORG : OR2 port map (I1=>t_c1, I2=>t_c2, O=>C);

* Another Implementation (with or Operator)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY fadder IS

PORT( a, b, ci : IN std_logic;

co, s : OUT std_logic );

END fadder;

ARCHITECTURE struct OF fadder IS

COMPONENT hadder

PORT( a, b : IN std_logic;

c, s : OUT std_logic );

END COMPONENT;

signal c1, c2, s1 : std_logic;

BEGIN

U1 : hadder

PORT MAP ( a => a, b => b, c => c1, s => s1 );

U2 : hadder

PORT MAP ( a => s1, b => ci, c => c2, s => s );

co <= c2 OR c1;

END struct;

* 4Bit Ripple Carry Adder Implementation (URL)

1) Strcutural Modeling

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY adder_4bit IS

PORT( ci : IN std_logic;

a, b : IN std_logic_vector(3 DOWNTO 0);

co : OUT std_logic;

s : OUT std_logic_vector(3 DOWNTO 0) );

END adder_4bits;

ARCHITECTURE struct OF adder_4bits IS

COMPONENT fadder

PORT( a, b, ci : IN std_logic;

co, s : OUT std_logic );

END COMPONENT;

signal c0, c1, c2 : std_logic;

BEGIN

U1 : fadder

PORT MAP ( a => a(0), b => b(0), ci => ci, co => c0, s => s(0) );

U2 : fadder

PORT MAP ( a => a(1), b => b(1), ci => c0, co => c1, s => s(1) );

U3 : fadder

PORT MAP ( a => a(2), b => b(2), ci => c1, co => c2, s => s(2) );

U4 : fadder

PORT MAP ( a => a(3), b => b(3), ci => c2, co => co, s => s(3) );

END struct;

2) Data Flow Modeling

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY adder_4bit IS

PORT( ci : IN std_logic;

a, b : IN std_logic_vector(3 DOWNTO 0);

co : OUT std_logic;

s : OUT std_logic_vector(3 DOWNTO 0) );

END adder_4bit;

ARCHITECTURE behave OF adder_4bit IS

signal a_s, b_s, s_s : std_logic_vector(4 DOWNTO 0);

BEGIN

a_s <= '0' & a;

b_s <= '0' & b;

s_s <= a_s + b_s + ci;

co <= s_s(4);

s <= s_s(3 DOWNTO 0);

END behave;Test Bench (테스트 벤치)

- VHDL 코드에 테스트 입력을 적용하기 위한 코드이다.

- 시뮬레이션을 통해 설계의 타당성을 검증하기 위해 테스트 벤치로부터의 결과를 이용한다.

-- Entity Declaration

ENTITY FA_test Is

end FA_test;

-- Architecture Body

ARCHITECTURE Test OF FA_test IS

signal X, Y, Cin : bit;

signal S, C : bit;

component Full_Adder

port( X, Y, Cin : IN bit;

S, C : OUT bit );

end component

BEGIN

FA : Full_Adder port map( X, Y, Cin, S, C);

-- X,Y,Cin에 10ns 주기로 000부터 111까지 입력시킨다.

X <= '0',

'1' after 40 ns, '0' after 80 ns;

Y <= '0',

'1' after 20 ns, '0' after 40 ns,

'1' after 60 ns, '0' after 80 ns;

Cin <= '0',

'1' after 10 ns, '0' after 20 ns,

'1' after 30 ns, '0' after 40 ns,

'1' after 50 ns, '0' after 60 ns,

'1' after 70 ns, '0' after 80 ns;

end Test;- 본 테스트 벤치에서는 외부에서의 입출력이 없고, 자체적인 입력 파형을 통해 테스팅하기 때문에,

Entity Declaration 부분에서 \(\texttt{port}\)문을 필요로 하지 않는다.

* Configuration Declaration

-- Configuration Declaration

CONFIGURATION Full_Adder_Test_Config1 OF testbench_fa Is

for Test

for FA : Full_Adder

use ENTITY Work.Full_Adder(Structural_Design);

for Structural_Design

for HA1 : Half_Adder

use ENTITY Work.Half_Adder(Dataflow_Design);

end for;

for HA2 : Half_Adder

use ENTITY Work.Half_Adder(Behavioral_Design);

end for;

for ORG : OR2

use ENTITY Work.OR2(Dataflow_Design);

end for;

end for;

end for;

end for;

end Full_Adder_Test_Config1;

* Full Adder의 Simulation 결과