Delay Mechanism

지연 메커니즘

- VHDL에서는 Signal Assignment에 after 구문을 통해 Delay를 표현할 수 있다.

Inertial Delay (관성 지연)

- 입력 신호 레벨이 적어도 어느 시간폭 D 만큼 지속되는 경우에 한하여,

입력 신호의 변화가 시간 D만큼 늦춰져 출력에 나타는 지연이다.

- 기준치보다 짧은 Pulse가 입력된 경우, 이를 출력에 반영하지 않기 위해 고안된 개념이다.

(즉, Garbage Value 의 입력을 막기 위해, 입력의 변화를 인지하기 위한 시간을 정의하기 위해 고안되었다.)

- 관성 지연은 입력의 변화가 출력에 전달되기 위해 시간을 필요로 하는 경우에 사용되며,

일정 시간이 흘러야 그 구문이 평가된다는 것을 의미한다.

- 관성 지연은 VHDL에서 Default 로 지정되어 있어, 특별히 지정할 필요가 없다.

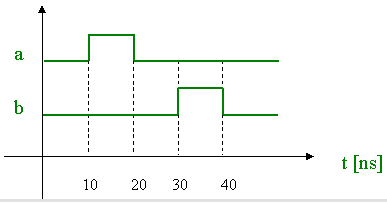

Example. Inertial Delay

b <= a AFTER 20 ns;- VHDL에서 Inertial Delay는 Default이므로, 별다른 구문이 필요하지 않다.

- 입력 a 가 10ns 만큼만 유지되었으므로, 이는 출력 b 에 반영되지 않는다.

(위 VHDL 구문에서 Inertial Delay로 20ns 만큼 정의되어 있음을 확인하자.)

Transport Delay (전달 지연)

- VHDL에서는 TRANSPORT 키워드를 통해 표현할 수 있다.

- PCB 회로의 배선에 의한 지연을 모델링하기 위해 고안된 개념이다.

- 단순히, 쓰여지는 동안의 시간을 입력신호에 추가하면 된다.

Example. Transport Delay

b <= TRANSPORT a AFTER 20 ns;- VHDL에서는 전달 지연을 구현하기 위해 키워드 TRANSPORT 를 사용해야 한다.

- 입력 a 가 입력되면 정의된대로, 10ns의 지연시간이 흐른 뒤, 출력 b 에 반영된다.

Simulation Delta

Example. Simulation Delta

ENTITY reg IS

PORT( a, clock : IN BIT;

d : OUT BIT );

END ref;

ARCHITECTURE delta_test OF reg IS

SIGNAL b, c : BIT;

BEGIN

b <= not(a);

c <= not(clock AND b);

d <= c AND b;

END delta_test;

-- Input Stimulus : clock = '1', a = '1' -> '0'

Delta and Non-Delta Delay Mechanism

- 아주 짧은 시간동안의 지연을 구현하기 위한 메커니즘이다.

* 임시 스크린샷

C <= A xnor B after 5ns